# **C2000 Digital Control Library**

Version 3.4

**User's Guide**

### Read This First

#### About This Manual

This User's Guide covers version 3.4 of the C2000 Digital Control Library (DCL). It contains technical descriptions of the library functions and how to use them. The DCL User's Guide does not cover control applications, control theory, or technical details of C2000 devices; however some information on these topics may be found in the references listed in chapter 6.

The User's Guide is divided into six chapters. Chapter 1 presents a general introduction to the library and provides background information. Chapter 2 describes the library contents and structure, how to add library functions to a user's program, and how to migrate existing source code. Chapter 3 describes the controllers and supporting functions, and provides information on their use. Chapter 4 describes the utilities supplied with the library, including data loggers, a transient capture module, and simulation models. Chapter 5 describes a set of supporting software examples which illustrate the use of the library. A list of relevant technical references and training can be found in Chapter 6.

#### How to Use This Manual

New users are advised to begin by reading the library overview in chapter 1. Chapter 2 provides a useful step-by-step guide of how to integrate the library into an existing C program as well as how to migrate from earlier versions, and should be read carefully by all users. Once the user has decided on the type of controller to implement, performance and other important information in the relevant sub-section of chapter 3 should be read carefully. If data array management or performance measurement is required, the utilities described in chapter 4 may be of interest. The library includes a number of software examples which illustrate the use of most of the controllers. These are described in chapter 5 and should serve as a good starting point for new users. Finally, for further reading and other resources, users are directed to the list of technical references and training materials in chapter 6.

#### Related Documentation from Texas Instruments

Technical documentation and development tools for the C2000 device can be found online on the Texas Instruments website at <a href="https://www.ti.com/c2000">www.ti.com/c2000</a>.

#### If You Need Assistance

Technical support for C2000 products is available online via the TI "E2E" Community: e2e.ti.com/support/microcontrollers/c2000

## **Contents**

| Road Th  | nis First                                         | iii |

|----------|---------------------------------------------------|-----|

|          | out This Manual                                   |     |

|          | v to Use This Manual                              |     |

|          |                                                   |     |

|          | ated Documentation from Texas Instruments         |     |

|          | ou Need Assistance                                |     |

|          | s                                                 |     |

|          |                                                   |     |

|          |                                                   |     |

|          | ction                                             |     |

|          | Supported Devices                                 |     |

|          | Overview of the Library                           |     |

| 1.3      | New In This Version                               | 3   |

|          | 1.3.1 New Features                                | 3   |

|          | 1.3.2 Bug Fixes                                   | 4   |

|          | 1.3.3 Function Naming                             |     |

|          | 1.3.4 Structure Naming                            |     |

|          | 1.3.5 Support Sub-structures                      |     |

|          | 1.3.6 Calling Convention                          |     |

|          | 1.3.7 Data Types                                  | 5   |

|          | 1.3.8 The ZPK3 Structure                          |     |

|          | 1.3.9 Compensator Stability Tests                 |     |

|          | 1.3.10 Deprecated Modules                         |     |

|          | CPU Compatibility                                 |     |

| 1.5      | Benchmarks                                        | 7   |

|          | 1.5.1 Controller Benchmarks                       |     |

|          | 1.5.2 Controller Support Function Benchmarks      |     |

|          | 1.5.3 Fast Update Function Benchmarks             |     |

|          | 1.5.4 FPU64 Function Benchmarks                   |     |

|          | ne Digital Control Library                        |     |

| 2.1      | What the Library Contains                         |     |

|          | 2.1.1 Header Files                                |     |

|          | 2.1.2 Source Files                                |     |

|          | 2.1.3 Examples                                    |     |

| 2.2      | Header File Dependency                            | 16  |

| 2.3      | How to Add the DCL to User Code                   |     |

|          | 2.3.1 Steps to Add the DCL to Existing C Code     |     |

|          | 2.3.2 Calling the Library Functions from Assembly |     |

| 2.4      | Updating Controller Parameters                    | 21  |

| 2.5      | Error Handling                                    | 23  |

|          | How to Modify the Library Code                    |     |

| Controll |                                                   |     |

|          | Linear PID Controllers                            | -   |

| <b>.</b> | 3.1.1 Description                                 |     |

|          | 3.1.2 Implementation                              |     |

|          | 3.1.3 Functions                                   |     |

| DCI      | l runPID C1                                       | 32  |

| DCL_runPID_C2                 | 32 |

|-------------------------------|----|

| DCL_runPID_C3                 | 33 |

| DCL_runPID_C4                 | 33 |

| DCL_runPID_L1                 | 34 |

| DCL_runPID_L2                 | 34 |

| DCL resetPID                  | 34 |

| DCL updatePID                 | 35 |

| DCL fupdatePID                |    |

| DCL setPIDfilterBW            |    |

| DCL_setActivePIDfilterBW      |    |

| DCL getPIDfilterBW            |    |

| DCL loadSeriesPIDasZPK        |    |

| DCL loadParallelPIDasZPK      |    |

| 3.2 Linear PI Controllers.    |    |

| 3.2.1 Description             |    |

| 3.2.2 Implementation          |    |

| 3.2.3 Functions               | 40 |

| DCL_runPI_C1                  | 40 |

| DCL_runPI_C2                  | 40 |

| DCL runPl C3                  | 40 |

| DCL runPl C4                  | 41 |

| DCL runPl C5                  |    |

| DCL runPl C6                  | 42 |

| DCL runPl C7                  | 42 |

| DCL runPI L1                  |    |

| DCL runPI L2                  |    |

| DCL runPI L3                  |    |

| DCL runPI L4                  |    |

| DCL runPI L5                  |    |

| DCL resetPl                   |    |

| DCL updatePI                  |    |

| DCL fupdatePI                 |    |

| DCL loadSeriesPlasZPK         |    |

| DCL loadParallelPlasZPK       |    |

| 3.3 Non-linear PID Controller |    |

| 3.3.1 Description             |    |

| 3.3.2 Implementation          |    |

| 3.3.3 Functions               |    |

| DCL_runNLPID_C1               |    |

| DCL_runNLPID_C2               |    |

| DCL runNLPID C3               |    |

| DCL setActiveNLPIDGamma       |    |

| DCL setNLPIDGamma             |    |

| DCL resetNLPID                |    |

| DCL updateNLPID               |    |

| DCL setActiveNLPIDfilterBW    |    |

| DCL setNLPIDfilterBW          |    |

| DCL_getNLPIDfilterBW          |    |

| DCL_getNLPIDgamma             |    |

| DCL_getNLPIDdelta             |    |

| 3.4 Non-linear PI Controllers |    |

|                               |    |

|     | 3.4.1       | Description                        |    |

|-----|-------------|------------------------------------|----|

|     | 3.4.2       | Implementation                     |    |

|     | 3.4.3       | Functions                          |    |

|     |             | LPI_C1                             |    |

|     |             | NLPI                               |    |

|     |             | teNLPI                             |    |

| 3.5 | Double      | e Integrator PI Controller         | 57 |

|     | 3.5.1       | Description                        | 57 |

|     | 3.5.2       | Implementation                     | 57 |

|     | 3.5.3       | Functions                          | 57 |

| DCL | _runPI      | /2_C1                              | 57 |

| DCL | _resetl     | PI2                                | 58 |

| DCL | updat       | tePI2                              | 58 |

| DCL | _ fupda     | atePI2                             | 59 |

| 3.6 | Direct      | Form 1 (First Order) Compensators  | 59 |

|     | 3.6.1       | Description                        |    |

|     | 3.6.2       | Implementation                     |    |

|     | 3.6.3       | Functions                          | 60 |

| DCL | _runDl      | F11_C1                             | 60 |

| DCL | _<br>_runDl | F11 C2                             | 60 |

|     | _           | F11¯L1                             |    |

|     |             | DF11                               |    |

|     | _           | teDF11                             |    |

|     |             | ateDF11                            |    |

|     | _ ′         | bleDF11                            |    |

|     |             | DF11asZPK                          |    |

|     |             | DF11asPI                           |    |

|     |             | Form 1 (Third Order) Compensators  |    |

| 0.7 | 3.7.1       | Description                        |    |

|     | 3.7.2       | Implementation                     |    |

|     | 3.7.3       | Functions                          |    |

| DCI |             | F13 C1                             |    |

|     |             | F13 C2                             |    |

|     |             | F13 C3                             |    |

|     |             | F13 C4                             |    |

|     |             | F13 C5                             |    |

|     | _           | F13_C6                             |    |

|     |             | F13_L1                             |    |

|     |             | F13_L1F13_L2                       |    |

|     |             |                                    |    |

|     |             | F13_L3                             |    |

|     |             | F13_L4                             |    |

|     | _           | F13_L5                             |    |

|     | _           | F13_L6                             |    |

|     | _           | DF13                               |    |

|     |             | teDF13                             |    |

|     | _ ′         | ateDF13                            |    |

|     | _           | bleDF13                            |    |

|     |             | DF13asZPK                          |    |

| 3.8 | Direct      | Form 2 (Second Order) Compensators | 73 |

|     | 3.8.1       | Description                        | 73 |

|     | 3.8.2       | Implementation                     |    |

|     | 3.8.3       | Functions                          | 75 |

| DCL_runDF22_C1                               | 75       |

|----------------------------------------------|----------|

| DCL_runDF22_C2                               | 75       |

| DCL runDF22 C3                               | 75       |

| DCL runDF22 C4                               | 76       |

| DCL runDF22 C5                               | 76       |

| DCL runDF22 C6                               | 76       |

| DCL runDF22 L1                               |          |

| DCL runDF22 L2                               |          |

| DCL runDF22 L3                               |          |

| DCL runDF22 L4                               |          |

| DCL resetDF22                                |          |

| DCL updateDF22                               |          |

| DCL fupdateDF22                              |          |

| DCL isStableDF22                             |          |

| DCL loadDF22asZPK                            |          |

| DCL loadDF22asZwn                            |          |

| DCL loadDF22asParallelPID                    |          |

| DCL loadDF22asSeriesPID                      |          |

| 3.9 Direct Form 2 (Third Order) Compensators |          |

| 3.9.1 Description                            |          |

| 3.9.2 Implementation                         |          |

| 3.9.3 Functions                              | 83       |

| DCL_runDF23_C1                               | 83       |

| DCL_runDF23_C2                               | 84       |

| DCL_runDF23_C3                               | 84       |

| DCL_runDF23_C4                               | 84       |

| DCL_runDF23_C5                               | 85       |

| DCL_runDF23_C6                               | 85       |

| DCL_runDF23_L1                               | 85       |

| DCL_runDF23_L2                               | 86       |

| DCL_runDF23_L3                               | 86       |

| DCL_resetDF23                                |          |

| DCL_updateDF23                               | 87       |

| DCL_fupdateDF23                              | 87       |

| DCL_isStableDF23                             | 87       |

| DCL_loadDF23asZPK                            | 88       |

| 3.10 Fixed-Point PID Controllers             | 88       |

| 3.10.1 Description                           |          |

| 3.10.2 Implementation                        |          |

| 3.10.3 Functions                             |          |

| DCL_runPID_A1                                |          |

| DCL_resetPID32                               |          |

| DCL_updatePID32                              |          |

| DCL_fupdatePID32                             |          |

| 3.11 Fixed-Point PI Controllers              |          |

| 3.11.1 Description                           |          |

| 3.11.2 Implementation                        |          |

| 3.11.3 Functions                             |          |

| DCL_runPI_A1                                 |          |

| DCL_resetPl32                                |          |

| DCL_updatePI32 DCL_fupdatePI32               | 94<br>94 |

| TO A TODO PROPERTY                           | 94       |

| 3.12 Gain Scheduler Module                |     |

|-------------------------------------------|-----|

| 3.12.1 Description                        | 94  |

| 3.12.2 Implementation                     | 95  |

| 3.12.3 Functions                          | 96  |

| DCL runGSM C1                             | 96  |

| DCL resetGSM                              | 96  |

| DCL updateGSM                             |     |

| DCL fupdateGSM                            |     |

| DCL loadGSMoffsets                        |     |

|                                           |     |

| DCL_loadGSMgains                          |     |

| 3.13 Non-linear Control Law               |     |

| 3.13.1 Description                        |     |

| 3.13.2 Implementation                     |     |

| 3.13.3 Functions                          |     |

| DCL_runNLF_C1                             |     |

| 3.14 Double Precision PID Controllers     |     |

| 3.14.1 Description                        |     |

| 3.14.2 Implementation                     |     |

| 3.14.3 Functions                          |     |

| DCL_runPIDF64_S1                          |     |

| DCL_resetPIDF64                           | 99  |

| DCL_updatePIDF64                          | 99  |

| DCL setPIDF64filterBW                     |     |

| DCL setActivePIDF64filterBW               |     |

| DCL_getPIDF64filterBW                     |     |

| 3.15 Double Precision DF22 Compensators   |     |

| 3.15.1 Description                        | 101 |

| 3.15.2 Implementation                     |     |

| 3.15.3 Functions                          |     |

| DCL runDF22F64 S1                         |     |

| DCL_runDF22F64_S2                         |     |

|                                           |     |

| DCL_runDF22F64_S3                         |     |

| DCL_resetDF22F64                          |     |

| DCL_updateDF22F64                         |     |

| Utilities                                 |     |

| 4.1 Control Clamps                        |     |

| 4.1.1 Description                         |     |

| 4.1.2 Functions                           | 105 |

| DCL_runClamp_C1                           | 105 |

| DCL_runClamp_C2                           | 105 |

| DCL runClamp L1                           |     |

| DCL_runClamp_S1                           |     |

| 4.2 Floating Point Data Logging Functions |     |

| 4.2.1 Description                         |     |

| 4.2.2 Functions                           |     |

| DCL deleteLog                             |     |

| <b>_</b>                                  |     |

| DCL_resetLog                              |     |

| DCL_initLog                               |     |

| DCL_writeLog                              |     |

| DCL_fillLog                               |     |

| DCL_clearLog                              | 110 |

| DCL_readLog                               | 110 |

|     | _copyLog                                |          |   |

|-----|-----------------------------------------|----------|---|

|     | _freadLog                               |          |   |

| DCL | _fwriteLog                              | 11       | 1 |

| 4.3 | 4-channel Floating Point Data Logger    |          |   |

|     | 4.3.1 Description                       |          |   |

|     | 4.3.2 Functions                         |          |   |

|     | _initMLOG                               |          |   |

|     | _resetMLOG                              |          |   |

|     | _armMLOG                                |          |   |

| DCL | _runMLOG                                | 11       | 4 |

| 4.4 | Transient Capture Module                |          |   |

|     | 4.4.1 TCM_idle Mode                     |          |   |

|     | 4.4.2 TCM_armed Mode                    |          |   |

|     | 4.4.3 TCM_capture Mode                  |          |   |

|     | 4.4.4 TCM_complete Mode                 |          |   |

| 501 | 4.4.5 Functions                         |          |   |

|     | _initTCM                                |          |   |

|     | _resetTCM                               |          |   |

|     | _armTCM                                 |          |   |

|     | _runTCM                                 |          |   |

| 4.5 | Performance Measurement                 |          |   |

|     | 4.5.1 Description                       |          |   |

| DC1 | 4.5.2 Functions                         |          |   |

|     | _runlES_C1                              |          |   |

|     | _runlES_C2                              |          |   |

|     | _runlAE_C1                              |          |   |

|     | _runlAE_C2                              |          |   |

|     | _runITAE_C1                             |          |   |

|     | runITAE_C2                              |          |   |

| 4.6 | Fixed Point Data Logger Support         |          |   |

|     | 4.6.1 Description                       |          |   |

| DC1 | 4.6.2 Functions                         |          |   |

|     |                                         |          |   |

|     | _resetLog32                             |          |   |

|     | _initLog32                              |          |   |

|     | _writeLog32                             |          |   |

|     | fillLog32                               |          |   |

|     | clearLog32                              |          |   |

|     | _readLog32                              |          |   |

|     | _copyLog32                              |          |   |

|     | _initMLOG32                             |          |   |

|     | _resetMLOG32                            |          |   |

|     | _armMLOG32                              |          |   |

|     | _runMLOG32                              |          |   |

| 4.7 | Simulation Models                       |          |   |

|     | 4.7.1 The DCL Block-set                 |          |   |

| 4.0 | 4.7.2 Simulation Example                |          |   |

| 4.გ | Double Precision Data Logging Functions |          |   |

|     | 4.8.1 Description                       |          |   |

| חכי | 4.8.2 Functions                         |          |   |

|     |                                         | 13<br>13 |   |

|     |            | initLog64                                                        |     |

|-----|------------|------------------------------------------------------------------|-----|

|     | DCL        | _writeLog64                                                      | 130 |

|     | DCL        | fillLog64                                                        | 131 |

|     | DCL        | clearLog64                                                       | 131 |

|     | DCL        | readLog64                                                        | 131 |

|     |            | <br>copyLog64                                                    |     |

| Exa |            | 28                                                               |     |

|     |            | Example 1: DF22 Compensator Running on FPU32                     |     |

|     | 0          | 5.1.1 Example Overview                                           |     |

|     |            | 5.1.2 Code Description                                           |     |

|     |            | 5.1.3 Running the Example                                        |     |

|     | 5.2        | Example 2: DF23 Compensator Running on CLA                       |     |

|     |            | 5.2.1 Example Overview                                           |     |

|     |            | 5.2.2 Code Description                                           |     |

|     |            | 5.2.3 Running the Example                                        |     |

|     | 5.3        | Example 3: NLPID Controller Running on FPU32                     | 138 |

|     |            | 5.3.1 Example Overview                                           |     |

|     |            | 5.3.2 Code Description                                           |     |

|     |            | 5.3.3 Running the Example                                        |     |

|     | 5.4        | Example 4: PI Controller Running on CLA                          |     |

|     |            | 5.4.1 Example Overview                                           |     |

|     |            | 5.4.2 Code Description                                           |     |

|     |            | 5.4.3 Running the Example                                        |     |

|     | 5.5        | Example 5: PID Controller Running on FPU32                       |     |

|     |            | 5.5.1 Example Overview                                           |     |

|     |            | 5.5.2 Code Description                                           |     |

|     |            | 5.5.3 Running the Example                                        |     |

|     | 5.6        | Example 6: TCM Running on FPU32                                  |     |

|     |            | 5.6.1 Example Overview                                           |     |

|     |            | 5.6.2 Code Description                                           |     |

|     |            | 5.6.3 Running the Example                                        |     |

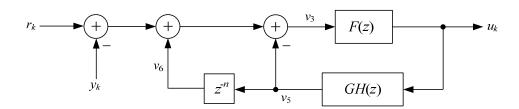

|     | 5.7        | Example 7: Smith Predictor Running on FPU32                      |     |

|     |            | 5.7.1 Example Overview                                           |     |

|     |            | 5.7.2 Code Description                                           |     |

|     | - 0        | 5.7.3 Running the Example                                        |     |

|     | 5.8        | Example 8: GSM Running on FPU32                                  |     |

|     |            | 5.8.1 Example Overview                                           |     |

|     |            | 5.8.2 Code Description                                           |     |

|     | <i>E</i> 0 | 5.8.3 Running the Example                                        |     |

|     | 5.9        | Example 9: Multiple Controller System with ERAD Running on FPU32 |     |

|     |            | 5.9.1 Example Overview                                           |     |

|     |            | 5.9.3 Running the Example                                        |     |

|     | 5 10       | Example 10: PID Running on FPU64                                 |     |

|     | 3.10       | 5.10.1 Example Overview                                          |     |

|     |            | 5.10.2 Code Description                                          |     |

|     |            | 5.10.3 Running the Example                                       |     |

|     | 5 11       | Example 11: NLPID Running on FPU32 (TMU1)                        |     |

|     | J. 1 1     | 5.11.1 Example Overview                                          |     |

|     |            | 5.11.2 Code Description                                          |     |

|     |            | 5.11.3 Running the Example                                       |     |

| Sun | port       |                                                                  |     |

|     |            | References                                                       |     |

|     | ٠          | 6.1.1 C2000 Documentation                                        |     |

|     |            |                                                                  |     |

|     | 6.1.2   | Literature | 154 |

|-----|---------|------------|-----|

| 6.2 | Trainin | g          | 155 |

|     |         | řt         |     |

# **Figures**

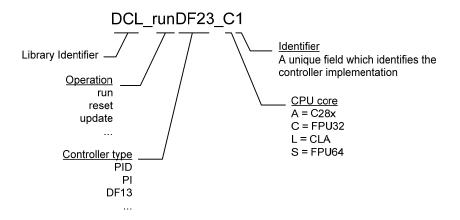

| Figure 1.  | DCL function naming                                      |      |

|------------|----------------------------------------------------------|------|

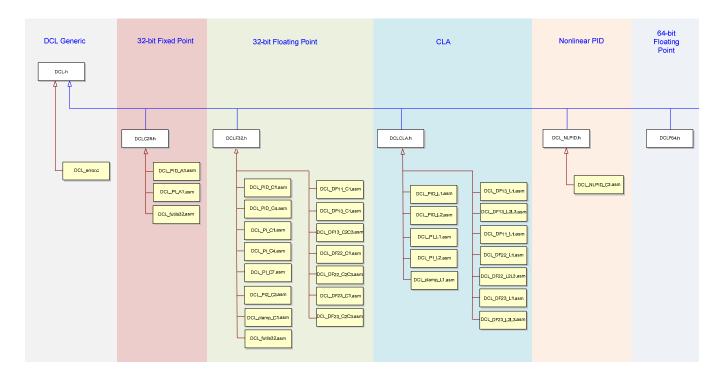

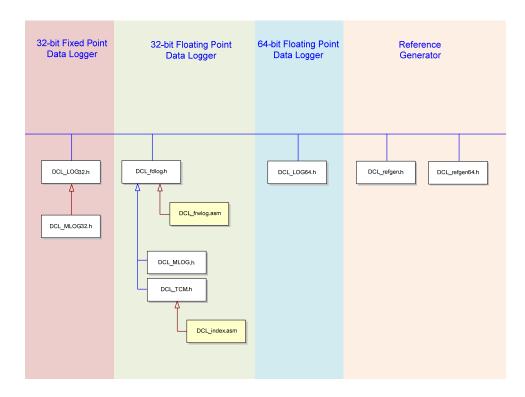

| Figure 2.  | DCL Controller Header File Dependency                    | . 17 |

| Figure 3.  | DCL Data Logger Header Dependency                        | . 17 |

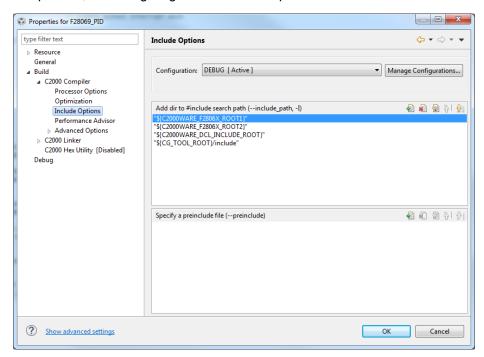

| Figure 4.  | CCSv6 Include Options                                    | . 19 |

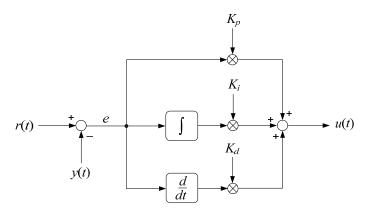

| Figure 5.  | Parallel form PID controller                             | . 28 |

| Figure 6.  | PID control action                                       | . 29 |

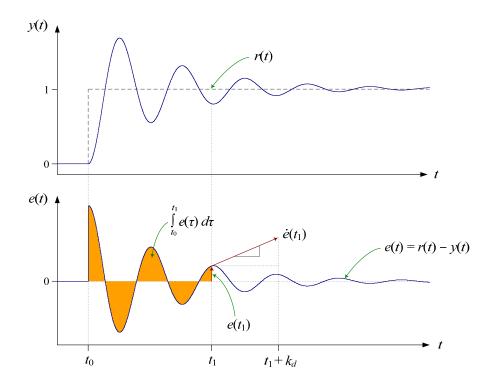

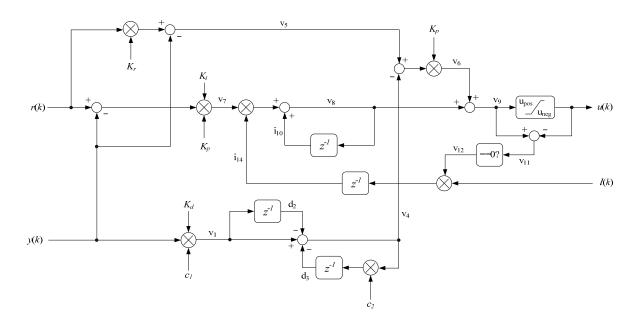

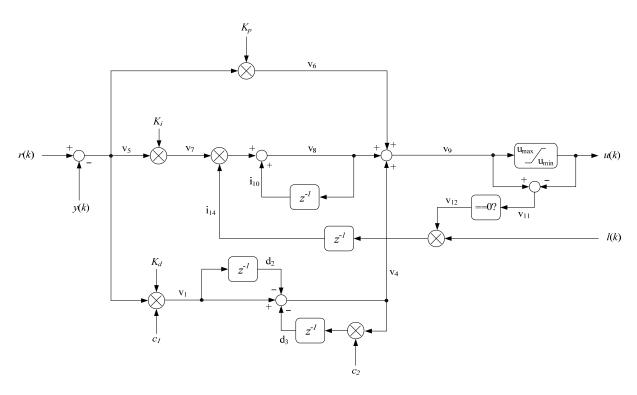

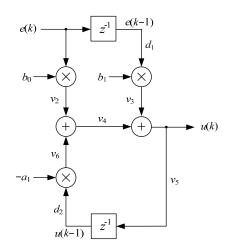

| Figure 7.  | DCL_PID C1, C2, & L1 architecture                        | . 31 |

| Figure 8.  | DCL_PID C3, C4, & L2 architecture                        | . 32 |

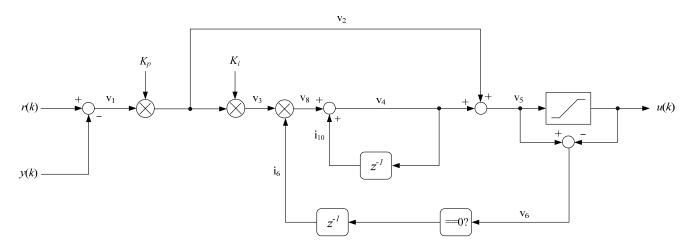

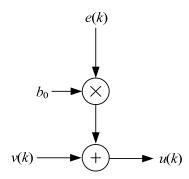

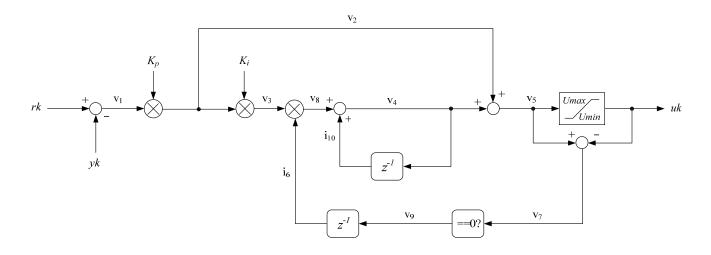

| Figure 9.  | DCL_PI C1, C2, L1, & L3 architecture                     | . 38 |

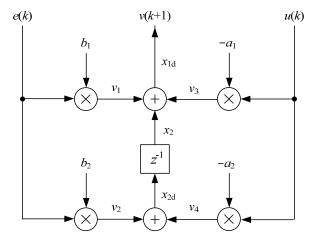

| Figure 10. | DCL_PI C3, C4, L2 & L4 architecture                      | . 38 |

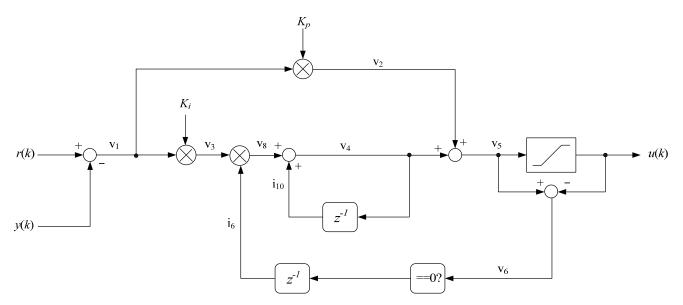

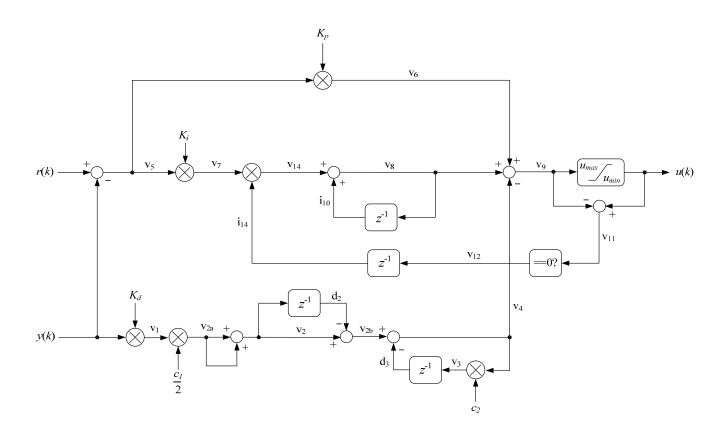

| Figure 11. | DCL_PI C5 architecture                                   | . 39 |

| Figure 12. | DCL_PI C6, C7, & L5 architecture                         | . 39 |

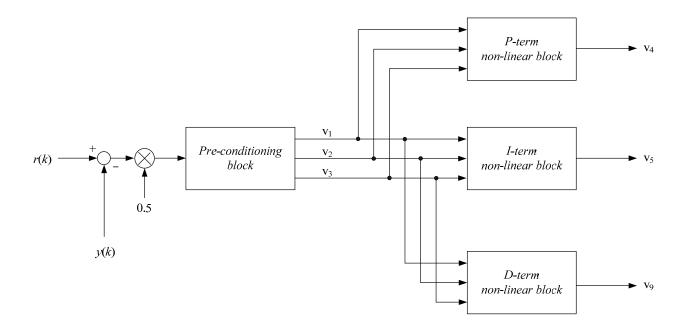

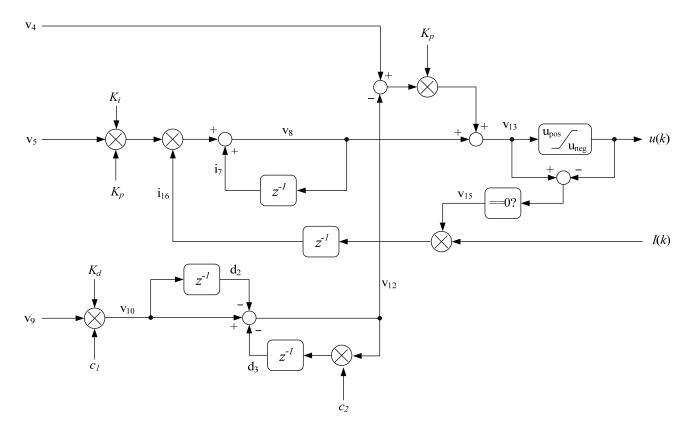

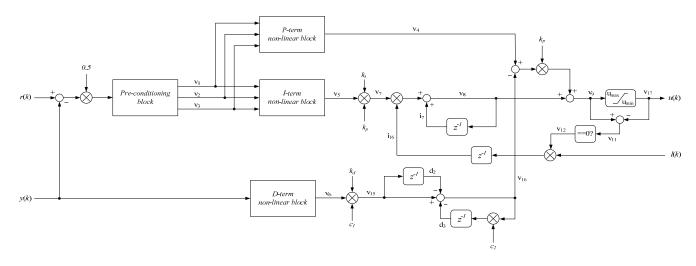

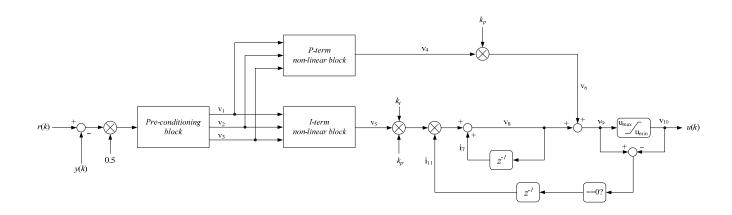

| Figure 13. | DCL_NLPID C1 input architecture                          | 46   |

| Figure 14. | DCL_NLPID C1 output architecture                         | 47   |

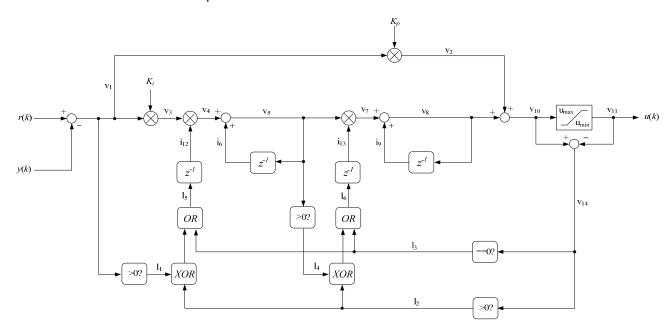

| Figure 15. | DCL_NLPID C2 & C3 architecture                           | 47   |

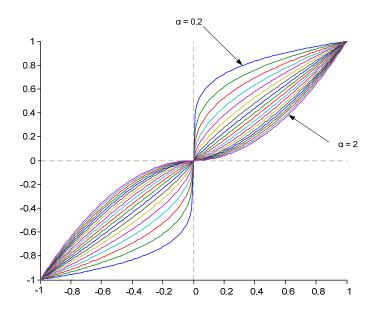

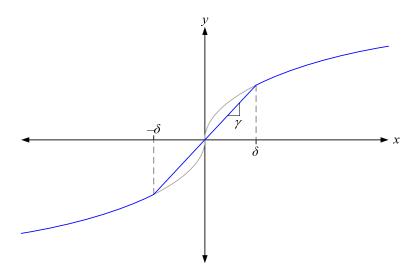

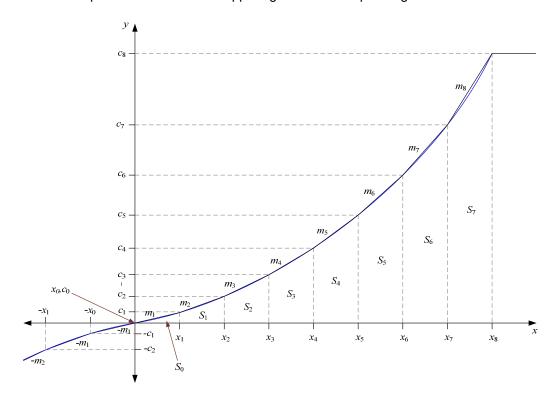

| Figure 16. | Non-linear control law input-output plot                 |      |

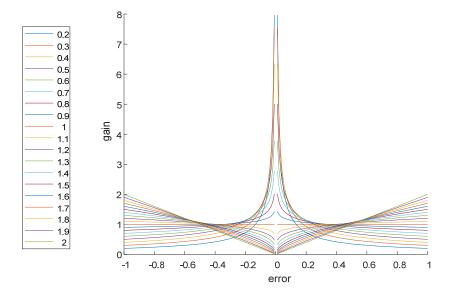

| Figure 17. | Gain vs error curves for varying alpha                   | 49   |

| Figure 18. | NLPID linearized region                                  | . 50 |

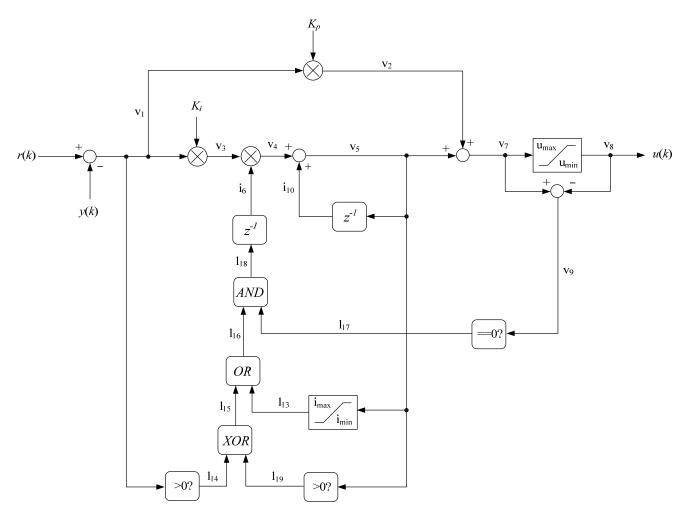

| Figure 19. | The DCL_NLPI_C1 architecture                             | . 55 |

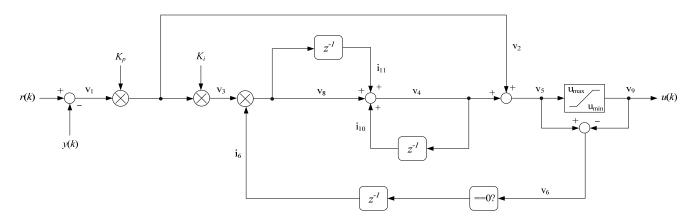

| Figure 20. | DCL_PI2 C1 architecture                                  |      |

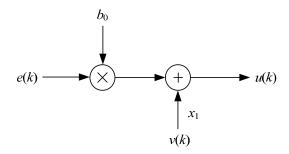

| Figure 21. | DCL_DF11 C1, C2, & L1 architecture                       | 60   |

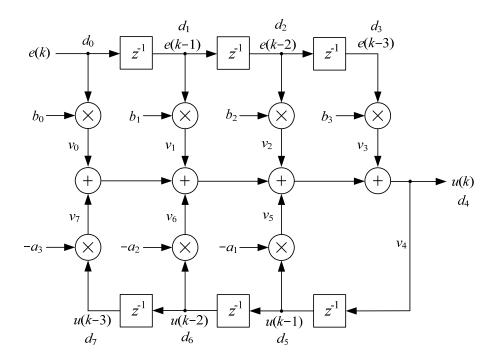

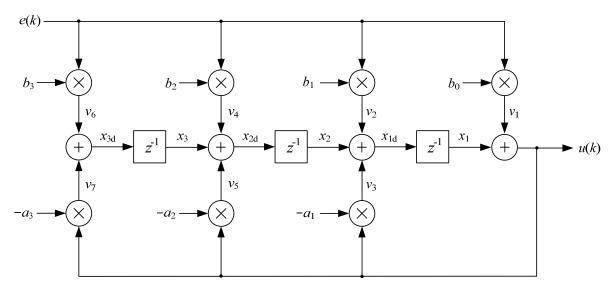

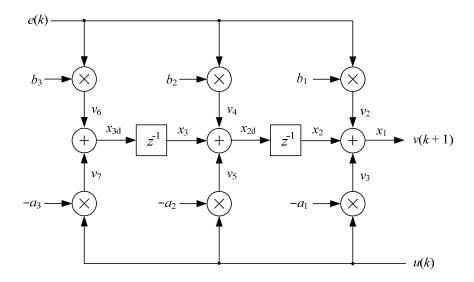

| Figure 22. | DCL_DF13 C1, C4, & L1 architecture                       |      |

| Figure 23. | DCL_DF13 C2, C3, C5, C6, L2, & L3 architecture           |      |

| Figure 24. | DCL_DF13 data & coefficient layout                       |      |

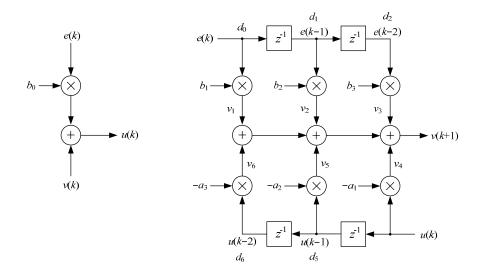

| Figure 25. | DCL_DF22 C1, C4,L1, & L4 architecture                    |      |

| Figure 26. | DCL_DF22 C2, C5, & L2 architecture                       |      |

| Figure 27. | DCL_DF22 C3, C6, & L3 architecture                       |      |

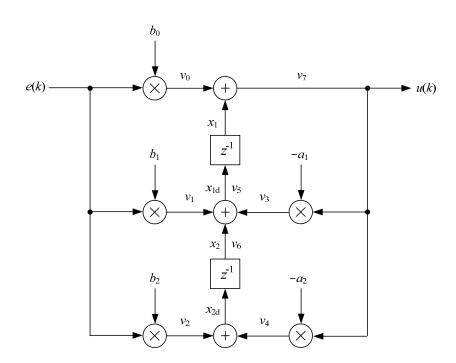

| Figure 28. | DCL_DF23 C1, C4, & L1 architecture                       |      |

| Figure 29. | DCL_DF23 C2, C5, & L2 architecture                       |      |

| Figure 30. | DCL_DF23 C3, C6, & L3 architecture                       |      |

| Figure 31. | DCL PID32 A1 architecture                                |      |

| Figure 32. | DCL PI A1 architecture                                   | . 93 |

| Figure 33. | DCL_GSM sector numbering                                 |      |

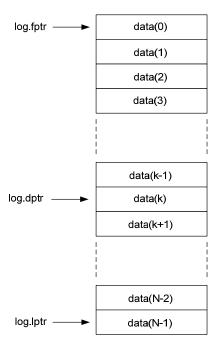

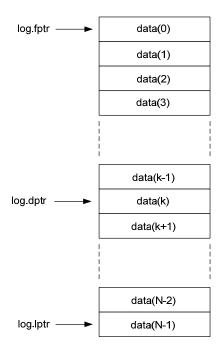

| Figure 34. | Data log pointer allocation                              |      |

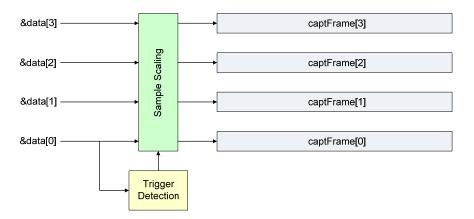

| Figure 35. | MLOG architecture                                        | 112  |

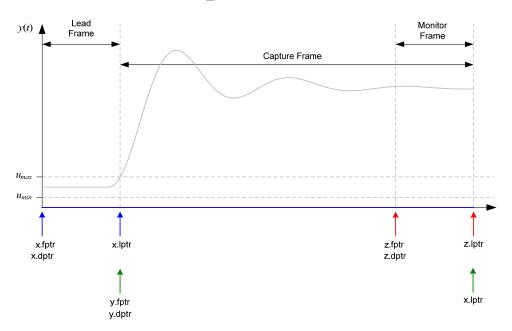

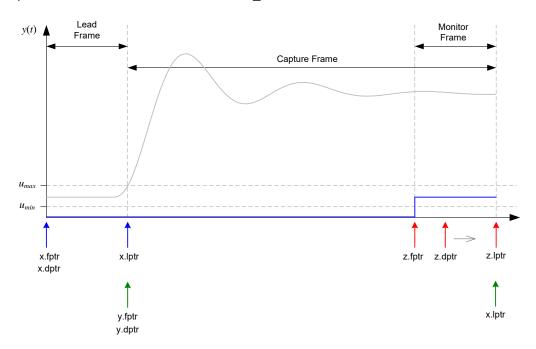

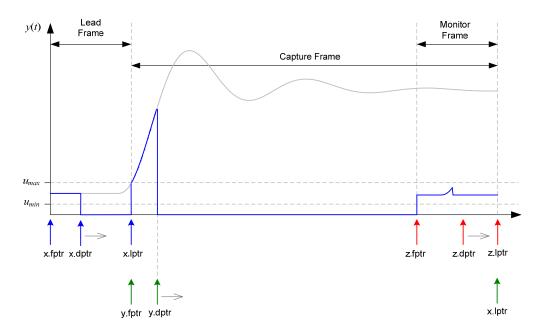

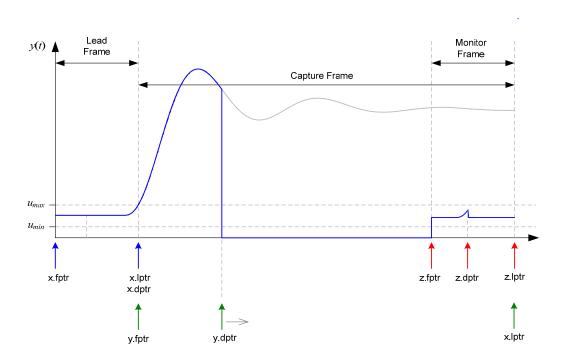

| Figure 36. | TCM operation in TCM_idle mode                           | 115  |

| Figure 37. | TCM operation in TCM_armed mode1                         |      |

| Figure 38. | TCM operation in capture mode (monitor frame un-winding) | 117  |

| Figure 39. | TCM operation in TCM_capture mode (lead frame complete)  | 117  |

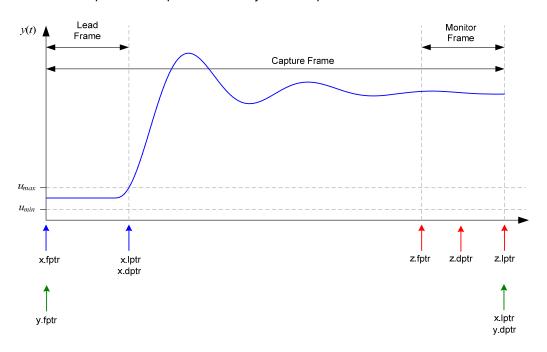

| Figure 40. | TCM capture complete                                     |      |

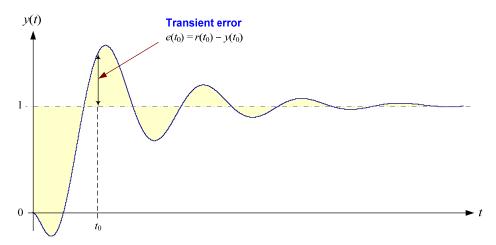

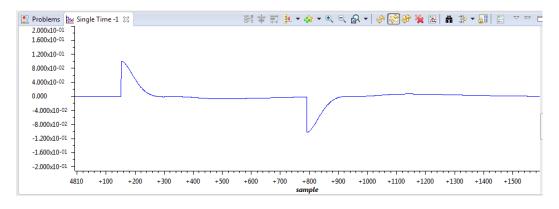

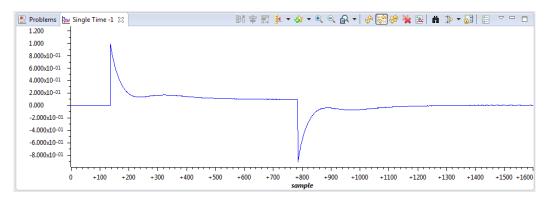

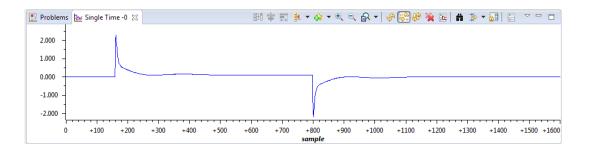

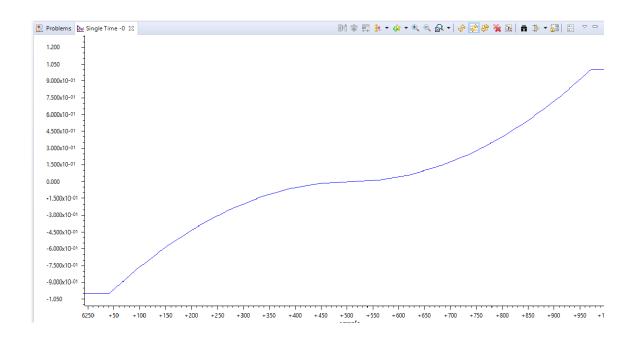

| Figure 41. | Transient servo error                                    |      |

| Figure 42. | FDLOG64 pointer allocation                               |      |

| Figure 43  |                                                          | 144  |

## **Tables**

| Table 1.  | CPU compatibility - controllers                                   | 6   |

|-----------|-------------------------------------------------------------------|-----|

| Table 2.  | CPU compatibility - support modules                               |     |

| Table 3.  | Controller execution & code size benchmarks                       |     |

| Table 4.  | Support function execution benchmarks                             |     |

| Table 5.  | Fast update function execution benchmarks                         |     |

| Table 6.  | Double precision function execution benchmarks (no optimization)  | 13  |

| Table 7.  | Double precision function execution benchmarks (-o2 optimization) |     |

| Table 8.  | List of DCL header files                                          |     |

| Table 9.  | List of DCL source files                                          | 15  |

| Table 10. | List of DCL code examples                                         | 16  |

| Table 11. | List of fast parameter update function execution cycles           | 23  |

| Table 12. | List of CSS enumerated error codes                                |     |

| Table 13. | Data log read/write benchmarks                                    | 108 |

| Table 14. | Performance index function benchmarks                             | 121 |

| Table 15. | FDLOG64 read/write benchmarks                                     | 129 |

|           |                                                                   |     |

### Introduction

This chapter contains a brief introduction to the Texas Instruments C2000 Digital Control Library (DCL).

#### Section

- 1.1 Supported Devices

- 1.2 Overview of the Library

- 1.3 New in this Version

- 1.4 Benchmarks

#### 1.1 Supported Devices

The DCL is compatible with four different C2000 CPUs:

- A 64-bit floating point CPU, denoted "FPU64"

- A 32-bit floating point CPU with trigonometric accelerator, denoted "FPU32"

- A 32-bit floating point "Control Law Accelerator", denoted "CLA"

- A 32-bit fixed point CPU, denoted "C28x"

Controller functions contain a suffix which identifies which CPU they are intended to be used with (see section 1.3.3). The following list provides an overview of the CPU availability on each class of C2000 device. Users should consult the datasheet for their chosen device to determine which CPU combination is present.

The FPU64 can be found on F2838x devices.

Among those devices which contain an FPU32 are:

- TMS320F28002x

- TMS320F28004x

- TMS320F2838x

- TMS320F2837x

- TMS320F2807x

- TMS320F2833x

- TMS320C2834x

1

- TMS320F2806x

- TMS320F28M35x

- TMS320F28M36x

Some FPU32 devices also contain a Trigonometric Math Unit (TMU) which extends the instruction set to provide support for trigonometric and other math operations. The DCL makes use of the TMU wherever possible. Refer to the controller descriptions for more information.

The library also includes functions optimized for use on the Control Law Accelerator (CLA). This CPU is only found on certain C2000 devices, including:

- TMS320F28004x

- TMS320F2838x

- TMS320F2837x

- TMS320F2807x

- TMS320F2806x

- TMS320F2805x

- TMS320F2803x

The DCL includes limited support for fixed-point C28x platforms in the form of two controllers and two data logging modules. Among the devices supported in this way are:

- TMS320F2805x

- TMS320F2804x

- TMS320F2803x

- TMS320F2802x

- TMS320F281x

- TMS320F280x

Fixed-point (C28x) DCL library functions will also run un-modified on any device which contains an FPU32. The DCL does not support the C24x CPU.

The C28x Run Time Support (RTS) library allows FPU32 functions written in C to be run on the fixed point C28x, however RTS emulation of the floating point data type is not cycle efficient and the library has not been tested in this way. Users are advised to run only those controller and CPU combinations recommended in this User's Guide. A list of controllers and compatible CPUs can be found in Table 1.

#### 1.2 Overview of the Library

The C2000 Digital Control Library (DCL) provides a suite of robust software functions for developers of digital control applications using the Texas Instruments C2000 MCU. All functions in the library are supplied in the form of C or assembly source code. There is no object code in the library. The library is deployed in the C2000Ware software suite, which is available for free download at: www.ti.com/tool/c2000ware.

The DCL functions are intended for use in any system in which a C2000 device is used. The DCL may not be used with any other devices. Refer to the C2000Ware license agreement for further information.

The DCL is independent of other application specific C2000 software libraries and Software Development Kits (SDKs), however providing attention is paid to data type and numerical range, integration with those packages is straightforward.

The DCL contains PID and "Direct Form" controller types. The former are typically used to tune properties of a transient response, while the latter are typically used to shape the open loop frequency response. The DCL contains functions to convert controller parameters from one type to the other; for example, the user may emulate PID control using a direct form 2 controller structure. The library also contains a gain scheduler module.

Supporting functions include: data logging, performance measurement, transient capture, and reference generation. Support functions run on the C28x, FPU32, or FPU64 only; they not compatible with the CLA. Most are supplied in C code form; however a small number of time-critical functions are also supplied as C callable assembly functions.

The library includes a set of example projects which illustrate how DCL functions might be applied in a user project. The library itself contains no device specific code and users of other C2000 devices will find it straightforward to apply the examples to their own projects.

The DCL does not contain tools to measure frequency response or perform compensator parameter selection; however similar features can be found in the "Compensation Designer" utility which is part of the TI "powerSUITE" package. A Software Frequency Response Analyzer (SFRA) utility can be found at: <a href="https://www.ti.com/tool/sfra">www.ti.com/tool/sfra</a>.

#### 1.3 New In This Version

#### 1.3.1 New Features

Version 3.4 of the DCL adds a reference generator module. The module is documented in a separate user's guide which can be found in the \docs sub-directory of the DCL installation path.

Also added in version 3.4 is support for the DF22 compensator in double precision floating point. The controller is designated DF22F64 and more information can be found in chapter 3. A double precision clamp has also been added to support this controller.

The macro DCL\_CLEAR\_ERROR\_CODE has been added to DCL.h to set the stored error in the CSS sub-structure to ERR\_NONE.

Controller update and run functions which are coded as static inline are now placed in the "dclfuncs" section using a CODE\_SECTION pragma. This allows time critical functions to be copied into RAM at run-time. This change has been made to the files: DCLF32.h, DCLF64.h, and DCL\_NLPID.h. Some functions in the new reference generator module are also placed in this section.

Library break-points now insert the ESTOP0 assembly instruction instead of NOP. This instruction inserts a software break-point so the user no longer has to manually set a break-point in CCS. In stand-alone mode, ESTOP0 is replaced by a NOP instruction. As before, break-points can be disabled by commenting out the definition of DCL BREAK POINTS ENABLED in DCL.h.

The C code in DCL\_error.c has been simplified. This code is intended for users to modify to implement their own custom error handlers.

The code in DCL\_NLPID\_C3.asm has been slightly modified. An attempt to build a project with this module included but without TMU support will now generate an error (rather than a warning) at compile time.

#### 1.3.2 Bug Fixes

Starting from version 3.4, the controller reset functions will no longer clear the error code in the CSS. This makes the reset functions compatible with situations in which the user does not wish to use the support sub-structures.

#### 1.3.3 Function Naming

No changes have been made to the function naming convention from v3.3.

The naming convention allows several controllers of similar type, but with different implementations, to be used together in the same program without conflict. An example of a library function name, together with a description of the constituent fields, is shown below.

Figure 1. DCL function naming

In this format, both the controller type and the CPU on which it runs are explicit. This allows future expansion of the library with variations of each controller type. An example is the PID controller, which exists in both "ideal" and "parallel" forms in the library. The final digit is an arbitrary number which identifies the implementation. Users may add their own controller variations to the DCL controllers by changing the final two characters of the function name. Refer to section 2.6 for further information.

In addition to "run", all control structures have associated "reset" and "update" functions. The first resets all internal non-parametric data to its default values without changing any controller parameters. The second performs a safe parameter update without changing any non-parametric control data. Note that the "update" function requires both SPS and CSS structures. The same "verb-noun" function name construction shown in Figure 1 applies to all supporting functions.

The DCL includes an implementation of a 64-bit floating point PID controller. This controller uses the letter "S" as the CPU identifier to distinguish it from the similar FPU32 controllers. It may be compiled and run on an FPU32, however without hardware support

for the double precision data type relatively poor cycle performance should be expected. Refer to Table 6 and Table 7 for further information.

#### 1.3.4 Structure Naming

No changes have been made to the structure naming convention from v3.3.

#### 1.3.5 Support Sub-structures

Each controller structure contains two 32-bit pointers, each of which holds the address of a separate support sub-structure.

The first such sub-structure contains a Shadow Parameter Set (SPS), which the user loads prior to executing a parameter update sequence. The update sequence performs a safe copy of the SPS parameters into the main controller structure by disabling interrupts before the copy sequence and re-enabling them afterwards. This ensures the controller never runs with a partially updated parameter set, and allows controller parameters to be updated without disturbing the control loop.

The second sub-structure is a Common Support Structure (CSS). The CSS contains supporting data used for error checking and parameter updates.

<u>The use of SPS and CSS is optional</u>. Users who do not need the additional features provided by SPS and CSS may safely ignore these structures.

#### 1.3.6 Calling Convention

All functions in the DCL are designed to be called from a C program. The context save & restore in each function assumes the standard parent register save is performed be the compiler. If any of the assembly functions are called from an assembly program, additional context save & restore instructions must be added by the user. See section 2.2.2 for further details.

#### 1.3.7 Data Types

Library floating-point variables are declared with either the  $float32\_t$  or the  $float64\_t$  data type. Unsigned and signed integers are declared as  $uint16\_t$  and  $int16\_t$  respectively. Fixed-point controllers use the signed long integer type  $int32\_t$ . Data type definitions can be found in the DCL.h header file. The DCL is compatible with both COFF and EABI compilers.

#### 1.3.8 The ZPK3 Structure

The library header file <code>DCL.h</code> contains a type definition of a third order transfer function in the form of zero and pole frequencies, and a real gain. This "ZPK3" structure enables direct form compensators to be configured from specifications involving pole and zero frequencies. Functions also exist to load PI and PID controllers in the same way. Refer to chapter 3 for more information on controller configuration using ZPK3.

The general form of the linear third order DT transfer function is

Equation 1.

$$F(z) = K \frac{(z-q1)(z-q2)(z-q3)}{(z-p1)(z-p2)(z-p3)}$$

In Equation 1, q1, q2, and q3, represent the frequencies of the three zeros in Hz; p1, p2, and p3 represent the frequencies of the three poles in Hz; and K is the real gain.

The ZPK3 structure is also used in the library to represent first and second order transfer functions. In each case, poles and zeros on the right being ignored. For example, in a 1-pole, 1-zero description, only K, q1, and p1 are relevant; the user function will ignore q2, q3, p2, & p3.

The DCL functions which take ZPK3 arguments allow complex poles and zeros providing they exist in conjugate pairs, thereby resulting in real polynomial coefficients. Error checking is built into those functions to ensure this is always the case.

#### 1.3.9 Compensator Stability Tests

The library contains functions to test stability of all direct form compensators. Stability is determined from the pole locations based on the transfer function denominator coefficients. Generic polynomial stability functions are found in the library header file DCL.h. In the first order case, determination is trivial. For second and third order compensators, the Jury array method is used. All stability test functions return the bool data type: 'true' if all compensator poles lie within the unit circle, otherwise 'false'.

#### 1.3.10 Deprecated Modules

All multi-channel data loggers (MLOG & MLOG32) will be removed in a future version of the library.

#### 1.4 CPU Compatibility

The tables below list the CPU compatibility of the controller and support structures in the DCL.

Table 1. CPU compatibility - controllers

| Controller | C28x | FPU32 | FPU64 | CLA |

|------------|------|-------|-------|-----|

| DCL_PID    | No   | Yes   | No    | No  |

| DCL_PI     | No   | Yes   | No    | No  |

| DCL_PI2    | No   | Yes   | No    | No  |

| DCL_NLPID  | No   | Yes   | No    | No  |

| DCL_NLPI   | No   | Yes   | No    | No  |

| DCL_DF11   | No   | Yes   | No    | No  |

| DCL_DF13   | No   | Yes   | No    | No  |

| DCL_DF22   | No   | Yes   | No    | No  |

| DCL_DF23   | No   | Yes   | No    | No  |

| DCL_GSM      | No  | Yes | No  | No  |

|--------------|-----|-----|-----|-----|

| DCL_PID_CLA  | No  | No  | No  | Yes |

| DCL_PI_CLA   | No  | No  | No  | Yes |

| DCL_DF11_CLA | No  | No  | No  | Yes |

| DCL_DF13_CLA | No  | No  | No  | Yes |

| DCL_DF22_CLA | No  | No  | No  | Yes |

| DCL_DF23_CLA | No  | No  | No  | Yes |

| DCL_PID32    | Yes | No  | No  | No  |

| DCL_PI32     | Yes | No  | No  | No  |

| DCL_PIDF64   | No  | Yes | Yes | No  |

#### Table 2. CPU compatibility – support modules

| Controller | C28x | FPU32 | FPU64 | CLA |

|------------|------|-------|-------|-----|

| FDLOG      | No   | Yes   | No    | No  |

| MLOG       | No   | Yes   | No    | No  |

| ТСМ        | No   | Yes   | No    | No  |

| FDLOG32    | Yes  | No    | No    | No  |

| MLOG32     | Yes  | No    | No    | No  |

| FDLOG64    | No   | Yes   | Yes   | No  |

#### 1.5 Benchmarks

#### 1.5.1 Controller Benchmarks

Table 3 lists the performance of each library function by cycle count and code size. In all cases, cycle count benchmarks were measured by logging a free-running PWM timer before and after each function call. Therefore the measured cycle count includes the function calling overhead from the C environment. In cases where the cycle count is dependent on input data, such as in anti-windup logic, the maximum figure is always given. Compiler optimization was disabled in all tests. Function sizes are given in units of 16-bit words, as reported in the ".map" file.

#### Table 3. Controller execution & code size benchmarks

| Function      | Cycles | Size (W) |

|---------------|--------|----------|

| DCL_runPID_A1 | 99     | 80       |

| DCL_runPID_C1   | 83                    | 99                  |

|-----------------|-----------------------|---------------------|

| DCL_runPID_C2   | 197                   | 207                 |

| DCL_runPID_C3   | 186                   | 196                 |

| DCL_runPID_C4   | 86                    | 92                  |

| DCL_runPID_L1   | 53                    | 70                  |

| DCL_runPID_L2   | 45                    | 58                  |

| DCL_runPI_A1    | 62                    | 46                  |

| DCL_runPI_C1    | 52                    | 54                  |

| DCL_runPI_C2    | 117                   | 121                 |

| DCL_runPI_C3    | 122                   | 126                 |

| DCL_runPI_C4    | 48                    | 37                  |

| DCL_runPI_C5    | 194                   | 180                 |

| DCL_runPI_C6    | 140                   | 133                 |

| DCL_runPI_C7    | 51                    | 40                  |

| DCL_runPI_L1    | 34                    | 42                  |

| DCL_runPI_L2    | 33                    | 40                  |

| DCL_runPI_L3    | 118                   | 238                 |

| DCL_runPI_L4    | 122                   | 248                 |

| DCL_runPI_L5    | 138                   | 272                 |

| DCL_runNLPID_C1 | 284 <sup>(1)(2)</sup> | 312                 |

| DCL_setGamma    | 2090 <sup>(2)</sup>   |                     |

| DCL_runNLPID_C2 | 3353 <sup>(1)</sup>   | 3297 <sup>(1)</sup> |

| DCL_runNLPID_C3 | 117                   | 185                 |

| DCL_runNLPI     | 2230 <sup>(1)</sup>   | 2197 <sup>(1)</sup> |

| DCL_runPI2_C1   | 218                   | 201                 |

| DCL_runDF11_C1  | 37                    | 23                  |

| DCL_runDF11_C2  | 60                    |                     |

| DCL_runDF11_L1  | 30                    | 34                  |

| DCL_runDF13_C1  | 71                    | 66                  |

| DCL_runDF13_C2  | 20                    | 79                  |

| DCL_runDF13_C3  | 74                    | , ,                 |

| DCL_runDF13_C4  | 175                   | 162                 |

| DCL_runDF13_C5  | 40                    | 38                  |

| DCL_runDF13_C6  | 121                   | 126                 |

| DCL_runDF13_L1  | 61                    | 86                  |

| DCL_runDF13_L2  | 20                    | 100                 |

| DCL_runDF13_L3  | 58                    |                     |

| DCL_runDF22_C1  | 44                    | 45                  |

| DCL_runDF22_C2  | 19                    | 48                  |

| DCL runDF22 C3  |                       |                     |

| DCL_IUIDI 22_C3 | 39                    |                     |

| DCL_runDF22_C5                  | 29                  | 26                  |

|---------------------------------|---------------------|---------------------|

| DCL_runDF22_C6                  | 60                  | 67                  |

| DCL_runDF22_L1                  | 33                  | 40                  |

| DCL_runDF22_L2                  | 20                  | 60                  |

| DCL_runDF22_L3                  | 34                  | 60                  |

| DCL_runDF22_L4                  | 83                  | 146                 |

| DCL_runDF23_C1                  | 62                  | 64                  |

| DCL_runDF23_C2                  | 20                  | 60                  |

| DCL_runDF23_C3                  | 54                  | 69                  |

| DCL_runDF23_C4                  | 98                  | 107                 |

| DCL_runDF23_C5                  | 29                  | 26                  |

| DCL_runDF23_C6                  | 82                  | 97                  |

| DCL_runDF23_L1                  | 44                  | 60                  |

| DCL_runDF23_L2                  | 20                  | 00                  |

| DCL_runDF23_L3                  | 44                  | 80                  |

| DCL_runGSM_C1                   | 50                  | TBD                 |

| DCL_runNLF_C1                   | 1075 <sup>(1)</sup> | 1075 <sup>(1)</sup> |

| DCL_runPIDF64_S1 <sup>(4)</sup> | 2840                | 310                 |

| DCL_writeLog                    | 48                  | N/A                 |

| DCL_readLog                     | 39                  | N/A                 |

| DCL_freadLog                    | 22                  | 11                  |

| DCL_fwriteLog                   | 22                  | 14                  |

| DCL_runClamp_C1                 | 28                  | 20                  |

| DCL_runClamp_C2                 | 71                  | 20                  |

| DCL_runClamp_L1                 | 25                  | 26                  |

| DCL_runITAE_C1                  | (3)                 | 60                  |

| DCL_runIAE_C1                   | (3)                 | 60                  |

| DCL_runIES_C1                   | (3)                 |                     |

<sup>&</sup>lt;sup>(1)</sup> All paths operating in linearized error region. For all paths in non-linear operation, total cycle count is approximately 1,433. See section 3.3.1 for more information.

#### 1.5.2 Controller Support Function Benchmarks

The table below shows execution benchmarks for the supporting functions new in v3.0 of the DCL. Execution figures include C function calling overhead. Separate measurements are given for update performed and not performed according to the sts flag status (see section 2.4). In all cases, compiler optimization was turned off.

$<sup>^{(2)}</sup>$  Measured with run-time library support for the powf () function.

<sup>(3)</sup> Cycle count depends on buffer length. Refer to section 3.4.1 for more information.

<sup>(4)</sup> Refer to Table 6.

Table 4. Support function execution benchmarks

| Function                  | File     | Cycles (1)  | Cycles <sup>(2)</sup> |

|---------------------------|----------|-------------|-----------------------|

| DCL_resetPID              | DCLF32.h | 85          | 85                    |

| DCL_updatePID             | DCLF32.h | 964 / 796   | 201 / 33              |

| DCL_setPIDfilterBW        | DCLF32.h | 1060        | 771                   |

| DCL_getPIDfilterBW        | DCLF32.h | 509         | 509                   |

| DCL_loadSeriesPIDasZPK    | DCLF32.h | 3226        | 2939                  |

| DCL_loadParallelPIDasZPK  | DCLF32.h | 2741        | 2454                  |

| DCL_resetPI               | DCLF32.h | 71          | 71                    |

| DCL_updatePI              | DCLF32.h | 326 / 191   | 166 / 33              |

| DCL_loadSeriesPlasZPK     | DCLF32.h | 668         | 306                   |

| DCL_loadParallelPlasZPK   | DCLF32.h | 433         | 71                    |

| DCL_resetPI2              | DCLCLA.h | 82          | 82                    |

| DCL_updatePI2             | DCLCLA.h | 267 / 179   | 131 / 33              |

| DCL_resetDF11             | DCLF32.h | 71          | 71                    |

| DCL_updateDF11            | DCLF32.h | 113 / 33    | 113 / 33              |

| DCL_isStableDF11          | DCLF32.h | 62 / 62     | 62 / 62               |

| DCL_loadDF11asPI          | DCLF32.h | 611         | 548                   |

| DCL_loadDF11asZPK         | DCLF32.h | 291         | 102                   |

| DCL_resetDF13             | DCLF32.h | 110         | 110                   |

| DCL_updateDF13            | DCLF32.h | 200 / 33    | 201 / 33              |

| DCL_isStableDF13          | DCLF32.h | 1532 / 1524 | 1532 / 1524           |

| DCL_loadDF13asZPK         | DCLF32.h | 5333        | 4962                  |

| DCL_resetDF22             | DCLF32.h | 72          | 72                    |

| DCL_updateDF22            | DCLF32.h | 144 / 33    | 144 / 33              |

| DCL_isStableDF22          | DCLF32.h | 794         | 794 / 793             |

| DCL_loadDF22asZPK         | DCLF32.h | 1419        | 1155                  |

| DCL_loadDF22asZwn         | DCLF32.h | 465         | 406                   |

| DCL_loadDF22asParallelPID | DCLF32.h | 1208        | 826                   |

| DCL_loadDF22asSeriesPID   | DCLF32.h | 1191        | 823                   |

| DCL_resetDF23             | DCLF32.h | 78          | 78                    |

| DCL_updateDF23            | DCLF32.h | 182 / 33    | 182 / 33              |

| DCL_loadDF23asZPK         | DCLF32.h | 7138        | 4950                  |

| DCL_isStableDF23          | DCLF32.h | 1531 / 1516 | 1531 / 1516           |

| DCL_resetPID32            | DCL32.h  | 52          | 52                    |

| DCL_updatePID32           | DCL32.h  | 154 / 34    | 154 / 34              |

| DCL_resetPI32             | DCL32.h  | 32          | 32                    |

| DCL_updatePI32            | DCL32.h  | 103 / 34    | 103 / 34              |

| DCL_resetGSM              | DCL.h    | 327         | 327                   |

| DCL_updateGSM             | DCL.h    | 504 / 33    | 504 / 33              |

| DCL_loadGSMgains            | DCL.h            | 389        | 389      |

|-----------------------------|------------------|------------|----------|

| DCL_loadGSMoffsets          | DCL.h            | 501        | 501      |

| DCL_runGSM_C1               | DCL.h            | 73 / 52    | 73 / 52  |

| DCL_fupdatePID              | DCL_futils.asm   | 77 / 37    | N/A      |

| DCL_fupdatePI               | DCL_futils.asm   | 64 / 37    | N/A      |

| DCL_fupdatePI2              | DCL_futils.asm   | 57 / 37    | N/A      |

| DCL_fupdateDF11             | DCL_futils.asm   | 58 / 37    | N/A      |

| DCL_fupdateDF13             | DCL_futils.asm   | 78 / 37    | N/A      |

| DCL_fupdateDF22             | DCL_futils.asm   | 66 / 37    | N/A      |

| DCL_fupdateDF23             | DCL_futils.asm   | 74 / 37    | N/A      |

| DCL_fupdateGSM              | DCL_futils.asm   | 114 / 37   | N/A      |

| DCL_fupdatePID32            | DCL_futils32.asm | 73 / 37    | N/A      |

| DCL_fupdatePI32             | DCL_futils32.asm | 57 / 37    | N/A      |

| DCL_resetNLPID              | DCL_NLPID.h      | 84         | 85       |

| DCL_updateNLPID             | DCL_NLPID.h      | 1190 / 871 | 353 / 33 |

| DCL_setNLPIDfilterBW        | DCL_NLPID.h      | 1066       | 771      |

| DCL_setActiveNLPIDfilterBW  | DCL_NLPID.h      | 1028       | 743      |

| DCL_getNLPIDfilterBW        | DCL_NLPID.h      | 509        | 509      |

| DCL_getNLPIDgamma           | DCL_NLPID.h      | 998        | 999      |

| DCL_getNLPIDdelta           | DCL_NLPID.h      | 1273       | 1274     |

| DCL_setNLPIDgamma           | DCL_NLPID.h      | 3284       | 3057     |

| DCL_getNLFgamma             | DCL_NLPID.h      | 995        | 995      |

| DCL_setActivePIDfilterBW    | DCLF32.h         | 1027       | 743      |

| DCL_resetPIDF64             | DCLF64.h         | 106        | 106      |

| DCL_updatePIDF64            | DCLF64.h         | 546 / 35   | 237 / 33 |

| DCL_setPIDF64filterBW       | DCLF64.h         | 10599      | 8132     |

| DCL_setActivePIDF64filterBW | DCLF64.h         | 10503      | 7982     |

| DCL_getPIDF64filterBW       | DCLF64.h         | 5163       | 5135     |

|                             |                  |            |          |

<sup>&</sup>lt;sup>(1)</sup> Built with no optimization and error checking enabled.

#### 1.5.3 Fast Update Function Benchmarks

The table below shows execution benchmarks for the fast update functions of the DCL. All functions are implemented in assembly code. The right-most column shows the number of CPU clock cycles for which global interrupts are disabled while the copy takes place. Interrupts are not disabled if an update is not pending and no update is performed.

Table 5. Fast update function execution benchmarks

| Function | File | Cycles   | Cycles      | Interrupts blocked |

|----------|------|----------|-------------|--------------------|

|          |      | (update) | (no update) | (cycles)           |

<sup>(2)</sup> Built with no optimization and error checking disabled.

| DCL_fupdatePID   | DCL_futils.asm   | 77  | 37 | 37 |

|------------------|------------------|-----|----|----|

| DCL_fupdatePI    | DCL_futils.asm   | 64  | 37 | 24 |

| DCL_fupdatePI2   | DCL_futils.asm   | 57  | 37 | 17 |

| DCL_fupdateDF11  | DCL_futils.asm   | 58  | 37 | 31 |

| DCL_fupdateDF13  | DCL_futils.asm   | 78  | 37 | 38 |

| DCL_fupdateDF22  | DCL_futils.asm   | 66  | 37 | 26 |

| DCL_fupdateDF23  | DCL_futils.asm   | 74  | 37 | 34 |

| DCL_fupdateGSM   | DCL_futils.asm   | 114 | 37 | 74 |

| DCL_fupdatePID32 | DCL_futils32.asm | 73  | 37 | 33 |

| DCL_fupdatePI32  | DCL_futils32.asm | 57  | 37 | 17 |

#### 1.5.4 FPU64 Function Benchmarks

The following two tables show execution benchmarks in CPU cycles for the double precision floating point functions of the DCL. In each case, figures for "fpu32" and "fpu64" settings of the "'—float\_support" compiler option are shown. The right-most column shows the percentage reduction in cycle count resulting from hardware support of the double precision data type.

Table 6. Double precision function execution benchmarks (no optimization)

| Function                     | fpu32 | fpu64 | Reduction (%) |

|------------------------------|-------|-------|---------------|

| DCL_setPIDF64filterBW        | 8090  | 174   | 97.85         |

| DCL_updatePIDF64             | 251   | 241   | 3.98          |

| DCL_updatePIDF64             | 55    | 55    | 0.00          |

| DCL_getPIDF64filterBW        | 5180  | 124   | 97.61         |

| DCL_setActivePIDF64filterBW  | 7998  | 154   | 98.07         |

| DCL_resetPIDF64              | 127   | 110   | 13.39         |

| DCL_runPIDF64                | 2840  | 275   | 90.32         |

| DCL_fillLog64 <sup>(1)</sup> | 573   | 534   | 6.81          |

| DCL_writeLog64               | 96    | 80    | 16.67         |

| DCL_readLog64                | 78    | 66    | 15.38         |

<sup>&</sup>lt;sup>(1)</sup> Data log size = 21 elements.

Table 7. Double precision function execution benchmarks (-o2 optimization)

| Function                     | fpu32 | fpu64 | Reduction (%) |

|------------------------------|-------|-------|---------------|

| DCL_setPIDF64filterBW        | 5141  | 76    | 98.52         |

| DCL_updatePIDF64             | 121   | 105   | 13.22         |

| DCL_updatePIDF64             | 22    | 22    | 0.00          |

| DCL_getPIDF64filterBW        | 5104  | 74    | 98.55         |

| DCL_setActivePIDF64filterBW  | 15    | 8     | 46.67         |

| DCL_resetPIDF64              | 35    | 35    | 0.00          |

| DCL_runPIDF64                | 2693  | 98    | 96.36         |

| DCL_fillLog64 <sup>(1)</sup> | 443   | 443   | 0.00          |

| DCL_writeLog64               | 32    | 30    | 6.25          |

| DCL_readLog64                | 32    | 26    | 18.75         |

<sup>&</sup>lt;sup>(1)</sup> Data log size = 21 elements.

**Chapter 2**

## **Using the Digital Control Library**

This chapter describes how to use the Digital Control Library.

#### Section

- 2.1 What the Library Contains

- 2.2 Header File Dependency

- 2.3 How to Add the DCL to User Code

- 2.4 Updating Controller Parameters

- 2.5 Error Handling

- 2.6 How to Modify the Library Code

#### 2.1 What the Library Contains

The DCL library is supplied entirely in source code form; there are no object or ".lib" files in the library. This allows the user to modify the library controller functions, or to add their own functions if different functionality is required. Controller functions are supplied in the following formats.

- Inline C code

- FPU32 assembly code

- C28x assembly code

- CLA assembly code

#### 2.1.1 Header Files

The following header files are included in the library.

#### Table 8. List of DCL header files

| Filename | Туре | Description                           |

|----------|------|---------------------------------------|

| DCL      | h    | Common library definitions            |

| DCLF32   | h    | FPU32 controller functions            |

| DCLF64   | h    | Double precision controller functions |

| DCLCLA   | h    | CLA controller functions              |

| DCLC28      | h | C28x fixed point controller functions |

|-------------|---|---------------------------------------|

| DCL_NLPID   | h | FPU32 non-linear PID                  |

| DCL_MLOG    | h | Four channel FPU32 data logger        |

| DCL_fdlog   | h | FPU32 data logger                     |

| DCL_fdlog64 | h | Double precision data logger          |

| DCL_TCM     | h | FPU32 Transient Capture Module        |

| DCL_log32   | h | C28x data logger functions            |

| DCL_MLOG32  | h | C28x four channel data logger         |

#### 2.1.2 Source Files

The following source files are included in the library.

Table 9. List of DCL source files

| Filename      | Туре | CPU                  | Description                      |

|---------------|------|----------------------|----------------------------------|

| DCL_PID_A1    | asm  | C28x                 | Fixed-point linear PID           |

| DCL_PID_C1    | asm  | FPU32                | Ideal linear PID                 |

| DCL_PID_C4    | asm  | FPU32                | Parallel linear PID              |

| DCL_PID_L1    | asm  | CLA                  | Ideal linear PID                 |

| DCL_PID_L2    | asm  | CLA                  | Parallel linear PID              |

| DCL_PI_A1     | asm  | C28x                 | Fixed-point linear PI            |

| DCL_PI_C1     | asm  | FPU32                | Ideal linear PI                  |

| DCL_PI_C4     | asm  | FPU32                | Parallel linear PI               |

| DCL_PI_C7     | asm  | FPU32                | Parallel linear PI (Tustin)      |

| DCL_PI_L1     | asm  | CLA                  | Ideal linear PI                  |

| DCL_PI_L2     | asm  | CLA                  | Parallel linear PI               |

| DCL_NLPID_C3  | asm  | FPU32 <sup>(1)</sup> | Nonlinear PID                    |

| DCL_DF11_C1   | asm  | FPU32                | Full DF1 (1 <sup>st</sup> order) |

| DCL_DF11_L1   | asm  | CLA                  | Full DF1 (1 <sup>st</sup> order) |

| DCL_DF13_C1   | asm  | FPU32                | Full DF1 (3rd order)             |

| DCL_DF13_C2C3 | asm  | FPU32                | Pre-computed DF1 (3rd order)     |

| DCL_DF13_L1   | asm  | CLA                  | Full DF1 (3rd order)             |

| DCL_DF13_L2L3 | asm  | CLA                  | Pre-computed DF1 (3rd order)     |

| DCL_DF22_C1   | asm  | FPU32                | Full DF2 (2nd order)             |

| DCL_DF22_C2C3 | asm  | FPU32                | Pre-computed DF2 (2nd order)     |

| DCL_DF22_L1   | asm  | CLA                  | Full DF2 (2nd order)             |

| DCL_DF22_L2L3 | asm  | CLA                  | Pre-computed DF2 (2nd order)     |

| DCL_DF23_C1   | asm  | FPU32                | Full DF2 (3rd order)             |

| DCL_DF23_C2C3 | asm  | FPU32                | Pre-computed DF2 (3rd order)     |

| DCL_DF23_L1   | asm  | CLA                  | Full DF2 (3rd order)             |

| DCL_DF23_L2L3 | asm  | CLA                  | Pre-computed DF2 (3rd order)     |

| DCL_frwlog    | asm  | FPU32                | Fast read/write log functions    |

| DCL_clamp_C1  | asm  | FPU32                | Data clamp                       |

| DCL_clamp_L1  | asm  | CLA                  | Data clamp                       |

|               |      |                      |                                  |

| DCL_index    | asm | FPU32 | Performance measurement |

|--------------|-----|-------|-------------------------|

| DCL_error    | С   | FPU32 | Template error handler  |

| DCL_futils   | asm | FPU32 | Fast parameter updates  |

| DCL futils32 | asm | C28x  | Fast parameter updates  |

<sup>(1)</sup> Requires TMU type 1. Refer to device datasheet for more information.

#### 2.1.3 Examples

A set of code examples is supplied with the Digital Control Library. These were prepared using CCS version 8.3.0 and run without modification on either the F28069, F280049, or F28388D device. The examples include linker command files which show how to allocate device memory when using the DCL. Further details can be found in Chapter 5.

#### Table 10. List of DCL code examples

| Example | Description                   | Core  | Device  |

|---------|-------------------------------|-------|---------|

| 1       | DF22 compensator              | FPU32 | F28069  |

| 2       | DF32 compensator              | CLA   | F28069  |

| 3       | NLPID controller              | FPU32 | F28069  |

| 4       | PI controller                 | CLA   | F28069  |

| 5       | PID controller                | FPU32 | F28069  |

| 6       | TCM                           | FPU32 | F28069  |

| 7       | Smith predictor               | FPU32 | F28069  |

| 8       | Gain scheduler                | FPU32 | F28069  |

| 9       | Multiple control loops + ERAD | FPU32 | F280049 |

| 10      | PID controller                | FPU64 | F28388D |

| 11      | NLPID controller              | FPU32 | F280025 |

#### 2.2 Header File Dependency

In the DCL, the file <code>DCL.h</code> is a central repository of common data types and sub-structure definitions. The naming convention in the DCL is that header files which contain basic controller functions for a specific CPU are named "<code>DCLxyz.h</code>", where "<code>xyz</code>" identifies the CPU designator and there is no underscore. Header files which contain specific controllers or utilities have an underscore immediately following the library designator, for example "<code>DCL\_NLPID.h</code>". Header file dependency is shown diagrammatically below.

Figure 2. DCL Controller Header File Dependency

Figure 3. DCL Data Logger Header Dependency

#### 2.3 How to Add the DCL to User Code

The Digital Control Library is intended to be used with a CCS project written in the C programming language. The user is responsible for initializing elements of the controller structure prior to calling the controller 'run' function. Typically the desired controller functions are inserted into an Interrupt Service Routine (ISR) triggered by a hardware event. This ensures that the controllers are executed at a fixed rate and that their timing is synchronized with the availability of incoming data. Control functions for use on the CLA would be called from a CLA task, which again, would typically be triggered at a fixed rate by a hardware event.

Controller parameters and dynamic data are encapsulated in a C structure, a pointer to which is passed as a parameter to the controller 'run' function. Typically, the controller structure would be a global variable in the user's program and its' contents initialized prior to the first call to the 'run' function. The controller 'run' functions are <u>not</u> re-entrant, since they rely on a global variable (in this case the controller structure). It is the responsibility of the user to ensure that a controller function is not called while a similar controller function is in progress.

#### 2.3.1 Steps to Add the DCL to Existing C Code

The following is a recommended sequence of steps to add the DCL to an existing C program. Refer to chapter 5 for code examples which illustrate configuration and use of the DCL with the CLA.

#### Step 1. Specify the include file(s)

Before you can begin using the library you must add the appropriate controller header file to your project.

To use the 32-bit floating-point DCL functions include the file DCLF32.h.

```

#include "DCLF32.h"

```

To use fixed-point CLA functions include the file DCLCLA.h.

```

#include "DCLCLA.h"

```

To use fixed-point DCL functions include the file DCLC28.h.

```

#include "DCLC28.h"

```

To use double precision floating point DCL functions include the file DCLF64.h.

```

#include "DCLF64.h"

```

To use any of the nonlinear controllers include the file <code>DCL\_NLPID.h.</code>

```

#include "DCL NLPID.h"

```

It is not necessary to explicitly include the common library file  $\mathtt{DCL}.h$  since that file is included in the controller header files above.

CCS must be configured in such a way that the DCL header files are visible to all program source files which reference controller variables or functions. The include file search options in CCS allow users to specify header file paths for each project. In CCS, the

include options can be configured by right-clicking on the project name, selecting "Properties", and navigating to the "Include Options" section.

#### Figure 4. CCSv6 Include Options

If you wish to use the data logger, MLOG, or TCM, you must also include the respective header file(s) (note that the MLOG and TCM modules include the relevant data log header file). Refer to section 2.2 for more information on header file dependency.

#### Step 2. Add the source files to the project

If you wish to use any of the assembly coded controllers, the source file(s) for the controller(s) you wish to use must be added to your CCS project. You can manually copy the files into your project directory, or specify the library pathname in the CCS compiler options. Refer to Table 9 for a list of controller source files. It is only necessary to add the source files for those functions you wish to use.

#### Step 3. Allocate the controller functions in the linker command file

DCL functions which run on the FPU32 or C28x core can be allocated to a specific memory block in the linker command file. It is common to place the controller functions in zero wait-state internal RAM since this allows them to run at the maximum speed of the device. Note that all CLA functions must run from internal zero wait-state RAM.

All DCL library functions are placed in the user defined code section .dclfuncs. An example showing how this section might be mapped into the internal L4 RAM memory block is shown below.

See also the linker command file F28069 DCL.cmd in the project examples (chapter 5).

In a stand-alone application, code must be stored in non-volatile memory (such as internal flash) and copied into RAM at run-time. For information on how to do this, refer to the

application note "Running an Application from Internal Flash Memory on the TMS320F28xxx DSP", TI literature number SPRA958.

Information on linker section allocation can be found in the "TMS320C28x Assembly Language Tools User's Guide".

#### Step 4. Create an instance of the controller

You must declare an instance of the controller you wish to use. For example, to create an initialized instance of a 32-bit floating-point PID controller with the name "pid1":

```

DCL PID pid1 = PID DEFAULTS;

```

This step will create an instance of a PID controller structure the elements of which are loaded with default parameter and data values specified in the file DCLF32.h.

Note that CLA variables must be initialized at run-time by user code (i.e. they cannot be initialized at the variable declaration). Typically this is done using a separate CLA task (see code examples 2 & 4).

#### Step 5. Create instances of the support structures (optional)

If you wish to make use of the error checking or safe parameter update features in the library, you must declare instances of both the SPS and CSS sub-structures, and initialize them appropriately. If you do not wish to use these features, this step can be ignored.

To declare an initialized instance of the SPS for the PID controller, you would do the following:

```

DCL PID SPS spid = PID SPS DEFAULTS;

```

To declare an initialized instance of the CSS for the PID controller, you would do the following:

```

DCL CSS cpid = DCL CSS DEFAULTS;

```

Assign each of the above structures to the PID control structure in step 4.

```

pid1.sps = &spid;

pid1.css = &cpid;

```

This creates a variable of type "DCL\_PID", the elements of which are initialized to default values specified in the <code>DCL.h</code> header file. Like any C variable, the structure must be visible to any source files which reference it.

Functions which use the update rate of the controller require the "T" element of the CSS sub-structure to be loaded in advance. This can be done using the DCL\_SET\_CONTROLLER\_PERIOD macro. For example, an update period of 100 ms would be loaded as follows:

```

DCL SET CONTROLLER PERIOD (pid1, 0.1f);

```

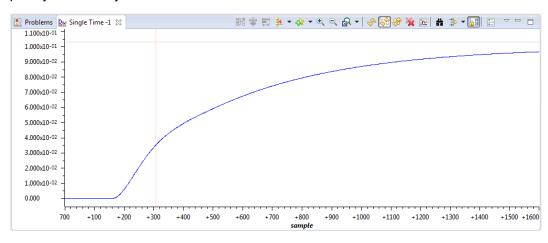

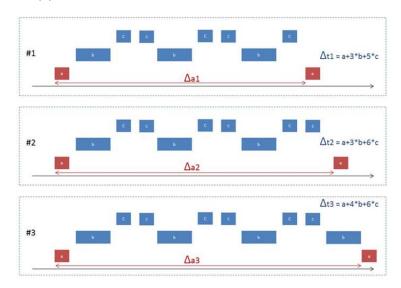

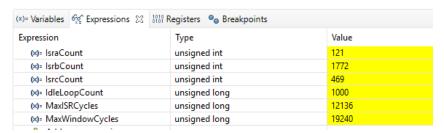

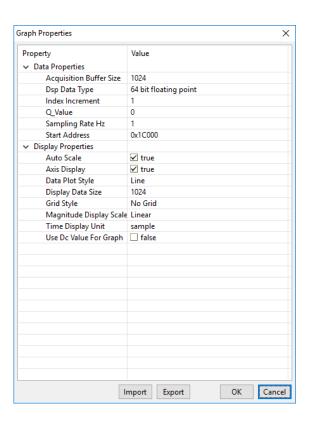

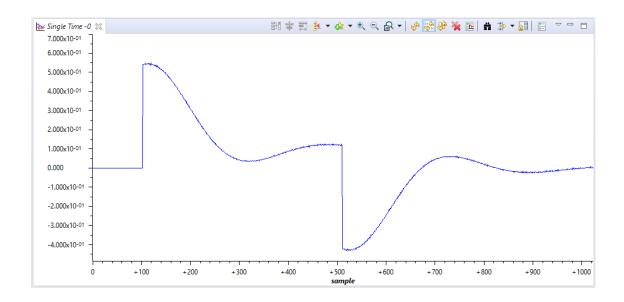

#### Step 6. Declare variables