|

xWRL684x MMWAVE-L-SDK

06.00.05

|

|

Features Supported

The SOC driver offers an API called SOC_clocksEnable that sets up and activates both PLL_DIG and ADPLL and configures r5, DSP clocks along with their multiplexers (MUXes).

- Note

- DSP frequency configured in SysConfig only configures the MUX for DSP. However, powering on the DSP is handled by RBL. Setting DSP frequency doesnot mean DSP is powered on.

This API configures:

- PLLDIG is configured to run at 400MHz and post divider is configured as 2 to get 200MHz.

- ADPLL is configured as below:

- 1600MHz - When DSP frequency is 400MHz or XTAL(40MHz).

- 1800MHZ - When DSP frequency is 450MHz or 360MHz.

- HS Divider Clock Out 0 is configured as source to fast clock 1 and is configured to 200MHz.

- HS Divider Clock Out 1 is configured as source to fast clock 2 and is configured as below:

- 400MHz - When DSP frequency is 400MHz.

- 450MHZ - When DSP frequency is 450MHz.

- 360MHZ - When DSP frequency is 360MHz.

- If DSP frequency is XTAL(40MHz), HS Divider Clock Out 1 and fast clock 1 are not configured.

- HS Divider Clock Out 2 to 50MHz.

- NOTE: This clock cannot be configured more than 600MHz hence ADPLL is used as the source clock for LVDS. However, though ADPLL is the source of LVDS, this clock has to be enabled for LVDS by design.

- HS Divider Clock Out 3 is configured as source to DSS domain and is configured to 200MHz.

- Fast clock 1 with post div 1 is selected as a source clock for R5 core. Hence, R5 core runs at 200MHz.

- DSP core clock source is set to:

- Fast Clock 2 with Div 1: When DSP frequency is 400MHz or 450MHz or 360MHz.

- XTAL(40MHz) with Div 1: When DSP frequency is XTAL(40MHz)

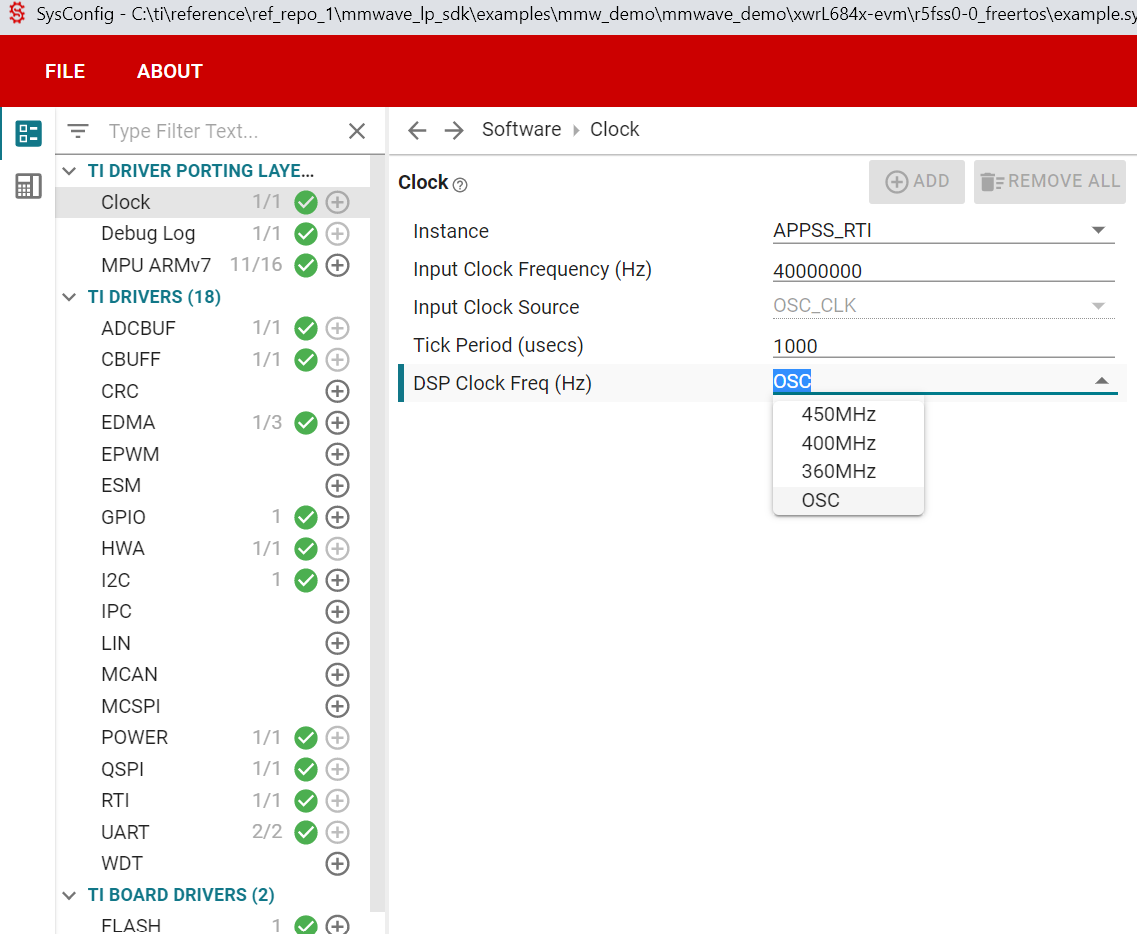

SysConfig Features

The SysCfg offers the ability to modify the clock speed of the DSP, as depicted in the below figure.

Example Usage

Include the below file to access the APIs

Configure Clocks

{

uint32_t hsdiv0FreqHz;

uint32_t hsdiv1FreqHz;

uint32_t hsdiv2FreqHz;

uint32_t hsdiv3FreqHz;

{

}

{

}

{

}

else

{

}

{

}

return status;

}

#define SOC_FastClk1Freq200MHz

Definition: soc.h:86

@ SOC_RcmADPllFoutFreqId_CLK_1600MHZ

Definition: soc_rcm.h:212

@ SOC_RcmPllFoutFreqId_CLK_400MHZ

Definition: soc_rcm.h:203

void SOC_TopssSelFclk2(SOC_TopssFclk2Source clkSrc)

#define SOC_C66CoreFreq360MHz

Definition: soc.h:84

#define SOC_RCM_FREQ_HZ2MHZ(hz)

Definition: soc.h:121

void SOC_rcmCoreDigPllConfig(SOC_RcmPllFoutFreqId, uint8_t)

void SOC_rcmCoreADPLLConfig(SOC_RcmADPllFoutFreqId outFreqId)

#define SOC_HsDivClkOut_360MHzFreq

Definition: soc.h:94

@ SOC_TopssFclk2Source_ADPLL_HSDIV_CLK1

Definition: soc_rcm.h:88

SOC_RcmADPllFoutFreqId

Definition: soc_rcm.h:211

#define SOC_HsDivClkOut_50MHzFreq

Definition: soc.h:90

#define SOC_HsDivClkOut_200MHzFreq

Definition: soc.h:91

#define SOC_RCM_XTAL_CLK_40MHZ

Definition: soc.h:95

#define SOC_R5FCoreFreq200MHz

Definition: soc.h:81

@ SOC_RcmDspClockSource_OSC_CLK

Definition: soc_rcm.h:110

#define SOC_C66CoreFreq400MHz

Definition: soc.h:82

@ SOC_RcmADPllHsDivClkOut0

Definition: soc_rcm.h:222

@ SOC_RcmDssClockSource_HSDIVCLKOUT3_CLK

Definition: soc_rcm.h:123

void SOC_rcmConfigureHsDividerClocks(SOC_RcmADPllHsDivClkOut HsDividerClkOutSel, uint32_t foutMHz, uint32_t finMHz)

@ SOC_RcmADPllHsDivClkOut2

Definition: soc_rcm.h:224

#define SOC_DSSFreq200MHz

Definition: soc.h:85

int32_t SOC_rcmSetDSSClock(uint32_t dssFreqHz, uint32_t inpFreqHz, SOC_RcmDssClockSource clkSrc)

#define SOC_C66CoreFreq450MHz

Definition: soc.h:83

@ SOC_RcmDspClockSource_FAST_CLK2

Definition: soc_rcm.h:111

#define SOC_HsDivClkOut_450MHzFreq

Definition: soc.h:93

#define SystemP_SUCCESS

Return status when the API execution was successful.

Definition: SystemP.h:56

int32_t SOC_rcmSetR5Clock(uint32_t r5FreqHz, uint32_t inpFreqHz, SOC_RcmR5ClockSource clkSrc)

@ SOC_TopssFclk1Source_ADPLL_HSDIV_CLK0

Definition: soc_rcm.h:75

SOC_RcmDspClockSource

DSP Clock Sources.

Definition: soc_rcm.h:109

void SOC_TopssSelFclk1(SOC_TopssFclk1Source clkSrc)

int32_t SOC_clocksEnable(uint32_t dspFreqHz)

Enable PLL Dig, ADPLL and set clocks for R5, C66, DSS, Fast Clock's and HSDIV's.

@ SOC_RcmADPllHsDivClkOut3

Definition: soc_rcm.h:225

#define SOC_HsDivClkOut_400MHzFreq

Definition: soc.h:92

@ SOC_RcmR5ClockSource_FAST_CLK1

Definition: soc_rcm.h:101

@ SOC_RcmADPllFoutFreqId_CLK_1800MHZ

Definition: soc_rcm.h:213

int32_t SOC_rcmSetDSPClock(uint32_t dspFreqHz, uint32_t inpFreqHz, SOC_RcmDspClockSource clkSrc)

@ SOC_RcmADPllHsDivClkOut1

Definition: soc_rcm.h:223