Functions | |

| static bool | IntMasterEnable (void) |

| Enables the processor interrupt. More... | |

| static bool | IntMasterDisable (void) |

| Disables the processor interrupt. More... | |

| void | IntRegister (uint32_t ui32Interrupt, void(*pfnHandler)(void)) |

| Registers a function to be called when an interrupt occurs. More... | |

| void | IntUnregister (uint32_t ui32Interrupt) |

| Unregisters the function to be called when an interrupt occurs. More... | |

| void | IntPriorityGroupingSet (uint32_t ui32Bits) |

| Sets the priority grouping of the interrupt controller. More... | |

| uint32_t | IntPriorityGroupingGet (void) |

| Gets the priority grouping of the interrupt controller. More... | |

| void | IntPrioritySet (uint32_t ui32Interrupt, uint8_t ui8Priority) |

| Sets the priority of an interrupt. More... | |

| int32_t | IntPriorityGet (uint32_t ui32Interrupt) |

| Gets the priority of an interrupt. More... | |

| void | IntEnable (uint32_t ui32Interrupt) |

| Enables an interrupt. More... | |

| void | IntDisable (uint32_t ui32Interrupt) |

| Disables an interrupt. More... | |

| void | IntPendSet (uint32_t ui32Interrupt) |

| Pends an interrupt. More... | |

| bool | IntPendGet (uint32_t ui32Interrupt) |

| Query whether an interrupt is pending. More... | |

| void | IntPendClear (uint32_t ui32Interrupt) |

| Unpends an interrupt. More... | |

| static void | IntPriorityMaskSet (uint32_t ui32PriorityMask) |

| Sets the priority masking level. More... | |

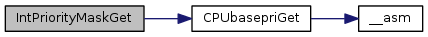

| static uint32_t | IntPriorityMaskGet (void) |

| Gets the priority masking level. More... | |

The interrupt controller API provides a set of functions for dealing with the nested vectored interrupt controller (NVIC). Functions are provided to enable and disable interrupts, register interrupt handlers, and set the priority of interrupts.

The event sources that trigger the interrupt lines in the NVIC are controlled by the MCU event fabric. All event sources are statically connected to the NVIC interrupt lines except one which is programmable. For more information about the MCU event fabric, see the MCU event fabric API.

The NVIC provides global interrupt masking, prioritization, and handler dispatching. Devices within the CC26xx family support 34 interrupt lines and 8 priority levels from 0 to 7 with 0 being the highest priority. Individual interrupt sources can be masked, and the processor interrupt can be globally masked as well (without affecting the individual source masks).

The NVIC is tightly coupled with the System CPU. When the processor responds to an interrupt, the NVIC supplies the address of the function to handle the interrupt directly to the processor.

Each interrupt source can be individually enabled and disabled through:

The global processor interrupt can be enabled and disabled with the following functions:

This does not affect the individual interrupt enable states. Masking of the processor interrupt can be used as a simple critical section (only an NMI can interrupt the processor while the processor interrupt is disabled), although masking the processor interrupt can have adverse effects on the interrupt response time.

It is possible to access the NVIC to see if any interrupts are pending and manually clear pending interrupts which have not yet been serviced or set a specific interrupt as pending to be handled based on its priority. Pending interrupts are cleared automatically when the interrupt is accepted and becomes active (being executed). The functions to read, clear, and set pending interrupts are:

The interrupt prioritization in the NVIC allows handling of higher priority interrupts before lower priority interrupts, as well as allowing preemption of lower priority interrupt handlers by higher priority interrupts. The priority of each interrupt source can be set and examined using:

Interrupts can be masked based on their priority such that interrupts with the same or lower priority than the mask are effectively disabled. This can be configured with:

Subprioritization is also possible; instead of having 3 bits of preemptable prioritization (8 levels), the NVIC can be configured for 3 - M bits of preemptable prioritization and M bits of subpriority. In this scheme, two interrupts with the same preemptable prioritization but different subpriorities do not cause a preemption; instead tail chaining is used to process the two interrupts back-to-back. If two interrupts with the same priority (and subpriority if so configured) are asserted at the same time, the one with the lower interrupt number is processed first. Subprioritization is handled by:

Interrupt handlers can be configured in one of two ways; statically at compile time or dynamically at run time. Static configuration of interrupt handlers is accomplished by editing the interrupt handler table in the startup code of the application. When statically configured, the interrupts must be explicitly enabled in the NVIC through IntEnable() before the processor can respond to the interrupt (in addition to any interrupt enabling required within the peripheral). Statically configuring the interrupt table provides the fastest interrupt response time because the stacking operation (a write to SRAM) can be performed in parallel with the interrupt handler table fetch (a read from Flash), as well as the prefetch of the interrupt handler (assuming it is also in Flash).

Alternatively, interrupts can be configured at runtime using (or the corresponding in each individual module API):

Registering an interrupt handler is a simple matter of inserting the handler address into the table. By default, the table is filled with pointers to an internal handler that loops forever; it is an error for an interrupt to occur when there is no interrupt handler registered to process it. Therefore, interrupt sources should not be enabled before a handler has been registered, and interrupt sources should be disabled before a handler is unregistered. When using IntRegister(), the interrupt must also be enabled as before; when using the function in each individual function API, IntEnable() is called by the driver and does not need to be called by the application. Run-time configuration of interrupts adds a small latency to the interrupt response time because the stacking operation (a write to SRAM) and the interrupt handler table fetch (a read from SRAM) must be performed sequentially.

Run-time configuration of interrupt handlers requires that the interrupt handler table is placed on a 1-kB boundary in SRAM (typically, this is at the beginning of SRAM). Failure to do so results in an incorrect vector address being fetched in response to an interrupt. The vector table is in a section called vtable and should be placed appropriately with a linker script.

| void IntDisable | ( | uint32_t | ui32Interrupt | ) |

Disables an interrupt.

The specified interrupt is disabled in the interrupt controller. Other enables for the interrupt (such as at the peripheral level) are unaffected by this function.

| ui32Interrupt | specifies the interrupt to be disabled. |

Definition at line 378 of file interrupt.c.

Referenced by CRYPTOAesEcbStatus(), CRYPTOAesLoadKey(), CRYPTOCcmAuthEncrypt(), CRYPTOCcmAuthEncryptStatus(), CRYPTOCcmInvAuthDecrypt(), CRYPTOCcmInvAuthDecryptStatus(), CRYPTOIntUnregister(), FlashIntUnregister(), I2CIntUnregister(), I2SIntUnregister(), IOCIntUnregister(), SSIIntUnregister(), TimerIntUnregister(), TRNGIntUnregister(), UARTIntUnregister(), uDMAIntUnregister(), and WatchdogIntUnregister().

| void IntEnable | ( | uint32_t | ui32Interrupt | ) |

Enables an interrupt.

The specified interrupt is enabled in the interrupt controller. Other enables for the interrupt (such as at the peripheral level) are unaffected by this function.

| ui32Interrupt | specifies the interrupt to be enabled. |

Definition at line 318 of file interrupt.c.

Referenced by CRYPTOAesCbc(), CRYPTOAesEcb(), CRYPTOCcmAuthEncrypt(), CRYPTOCcmInvAuthDecrypt(), CRYPTOIntRegister(), FlashIntRegister(), I2CIntRegister(), I2SIntRegister(), IOCIntRegister(), SSIIntRegister(), TimerIntRegister(), TRNGIntRegister(), UARTIntRegister(), uDMAIntRegister(), and WatchdogIntRegister().

|

inlinestatic |

Disables the processor interrupt.

Prevents the processor from receiving interrupts. This does not affect the set of interrupts enabled in the interrupt controller; it just gates the single interrupt from the controller to the processor.

true : Interrupts were already disabled when the function was called.false : Interrupts were enabled and are now disabled. Definition at line 159 of file interrupt.h.

|

inlinestatic |

Enables the processor interrupt.

Allows the processor to respond to interrupts. This does not affect the set of interrupts enabled in the interrupt controller; it just gates the single interrupt from the controller to the processor.

true : Interrupts were disabled and are now enabled.false : Interrupts were already enabled when the function was called. Definition at line 137 of file interrupt.h.

| void IntPendClear | ( | uint32_t | ui32Interrupt | ) |

Unpends an interrupt.

The specified interrupt is unpended in the interrupt controller. This will cause any previously generated interrupts that have not been handled yet (due to higher priority interrupts or the interrupt no having been enabled yet) to be discarded.

| ui32Interrupt | specifies the interrupt to be unpended. |

Definition at line 534 of file interrupt.c.

Referenced by CRYPTOAesCbc(), CRYPTOAesEcb(), CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| bool IntPendGet | ( | uint32_t | ui32Interrupt | ) |

Query whether an interrupt is pending.

This function will check whether the specified interrupt is pending in the interrupt controller. The interrupt must have been enabled for it to be called, so an interrupt can very well be pending waiting to be enabled or waiting for an interrupt of higher priority to be done executing.

| ui32Interrupt | specifies the interrupt to be queried. |

true : Specified interrupt is pending.false : Specified interrupt is not pending. Definition at line 491 of file interrupt.c.

| void IntPendSet | ( | uint32_t | ui32Interrupt | ) |

Pends an interrupt.

The specified interrupt is pended in the interrupt controller. This will cause the interrupt controller to execute the corresponding interrupt handler at the next available time, based on the current interrupt state priorities. For example, if called by a higher priority interrupt handler, the specified interrupt handler will not be called until after the current interrupt handler has completed execution. The interrupt must have been enabled for it to be called.

| ui32Interrupt | specifies the interrupt to be pended. |

Definition at line 438 of file interrupt.c.

| int32_t IntPriorityGet | ( | uint32_t | ui32Interrupt | ) |

Gets the priority of an interrupt.

This function gets the priority of an interrupt.

| ui32Interrupt | specifies the interrupt in question. |

Definition at line 298 of file interrupt.c.

| uint32_t IntPriorityGroupingGet | ( | void | ) |

Gets the priority grouping of the interrupt controller.

This function returns the split between preemptable priority levels and subpriority levels in the interrupt priority specification.

Definition at line 238 of file interrupt.c.

| void IntPriorityGroupingSet | ( | uint32_t | ui32Bits | ) |

Sets the priority grouping of the interrupt controller.

This function specifies the split between preemptable priority levels and subpriority levels in the interrupt priority specification. The range of the grouping values are dependent upon the hardware implementation; on the CC26xx family, three bits are available for hardware interrupt prioritization and therefore priority grouping values of three through seven have the same effect.

| ui32Bits | specifies the number of bits of preemptable priority. |

Definition at line 219 of file interrupt.c.

|

inlinestatic |

Gets the priority masking level.

This function gets the current setting of the interrupt priority masking level. The value returned is the priority level such that all interrupts of that and lesser priority are masked. A value of 0 means that priority masking is disabled.

Smaller numbers correspond to higher interrupt priorities. So for example a priority level mask of 4 will allow interrupts of priority level 0-3, and interrupts with a numerical priority of 4 and greater will be blocked.

The hardware priority mechanism will only look at the upper N bits of the priority level (where N is 3 for the CC26xx family), so any prioritization must be performed in those bits.

Definition at line 434 of file interrupt.h.

|

inlinestatic |

Sets the priority masking level.

This function sets the interrupt priority masking level so that all interrupts at the specified or lesser priority level are masked. This can be used to globally disable a set of interrupts with priority below a predetermined threshold. A value of 0 disables priority masking.

Smaller numbers correspond to higher interrupt priorities. So for example a priority level mask of 4 will allow interrupts of priority level 0-3, and interrupts with a numerical priority of 4 and greater will be blocked.

The hardware priority mechanism will only look at the upper N bits of the priority level (where N is 3 for the CC26xx family), so any prioritization must be performed in those bits.

| ui32PriorityMask | is the priority level that will be masked. |

Definition at line 408 of file interrupt.h.

| void IntPrioritySet | ( | uint32_t | ui32Interrupt, |

| uint8_t | ui8Priority | ||

| ) |

Sets the priority of an interrupt.

This function is used to set the priority of an interrupt. When multiple interrupts are asserted simultaneously, the ones with the highest priority are processed before the lower priority interrupts. Smaller numbers correspond to higher interrupt priorities; priority 0 is the highest interrupt priority.

The hardware priority mechanism will only look at the upper N bits of the priority level (where N is 3 for cc26xx), so any prioritization must be performed in those bits. The remaining bits can be used to sub-prioritize the interrupt sources, and may be used by the hardware priority mechanism on a future part. This arrangement allows priorities to migrate to different NVIC implementations without changing the gross prioritization of the interrupts.

| ui32Interrupt | specifies the interrupt in question. |

| ui8Priority | specifies the priority of the interrupt.

|

Definition at line 273 of file interrupt.c.

| void IntRegister | ( | uint32_t | ui32Interrupt, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers a function to be called when an interrupt occurs.

This function is used to specify the handler function to be called when the given interrupt is asserted to the processor. When the interrupt occurs, if it is enabled (via IntEnable()), the handler function will be called in interrupt context. Since the handler function can preempt other code, care must be taken to protect memory or peripherals that are accessed by the handler and other non-handler code.

| ui32Interrupt | specifies the interrupt in question. |

| pfnHandler | is a pointer to the function to be called. |

Definition at line 152 of file interrupt.c.

Referenced by CRYPTOIntRegister(), FlashIntRegister(), I2CIntRegister(), I2SIntRegister(), IOCIntRegister(), SSIIntRegister(), SysTickIntRegister(), TimerIntRegister(), TRNGIntRegister(), UARTIntRegister(), uDMAIntRegister(), and WatchdogIntRegister().

| void IntUnregister | ( | uint32_t | ui32Interrupt | ) |

Unregisters the function to be called when an interrupt occurs.

This function is used to indicate that no handler should be called when the given interrupt is asserted to the processor. The interrupt source will be automatically disabled (via IntDisable()) if necessary.

| ui32Interrupt | specifies the interrupt in question. |

Definition at line 200 of file interrupt.c.

Referenced by CRYPTOIntUnregister(), FlashIntUnregister(), I2CIntUnregister(), I2SIntUnregister(), IOCIntUnregister(), SSIIntUnregister(), SysTickIntUnregister(), TimerIntUnregister(), TRNGIntUnregister(), UARTIntUnregister(), uDMAIntUnregister(), and WatchdogIntUnregister().

| #define INT_PRI_LEVEL0 0x00000000 |

Definition at line 108 of file interrupt.h.

| #define INT_PRI_LEVEL1 0x00000020 |

Definition at line 109 of file interrupt.h.

| #define INT_PRI_LEVEL2 0x00000040 |

Definition at line 110 of file interrupt.h.

| #define INT_PRI_LEVEL3 0x00000060 |

Definition at line 111 of file interrupt.h.

| #define INT_PRI_LEVEL4 0x00000080 |

Definition at line 112 of file interrupt.h.

| #define INT_PRI_LEVEL5 0x000000A0 |

Definition at line 113 of file interrupt.h.

| #define INT_PRI_LEVEL6 0x000000C0 |

Definition at line 114 of file interrupt.h.

| #define INT_PRI_LEVEL7 0x000000E0 |

Definition at line 115 of file interrupt.h.

Referenced by IntPrioritySet().

| #define INT_PRIORITY_MASK 0x000000E0 |

Definition at line 107 of file interrupt.h.