|

|

|

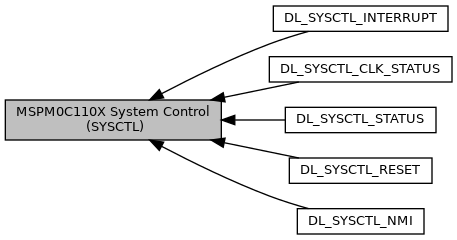

MSPM0C110X Driver Library

2.05.00.05

|

|

Modules | |

| DL_SYSCTL_RESET | |

| DL_SYSCTL_INTERRUPT | |

| DL_SYSCTL_NMI | |

| DL_SYSCTL_CLK_STATUS | |

| DL_SYSCTL_STATUS | |

Macros | |

| #define | DL_SYSCTL_setMCLKSource(current, next, ...) DL_SYSCTL_switchMCLKfrom##current##to##next(__VA_ARGS__); |

| Change MCLK source. More... | |

Functions | |

| __STATIC_INLINE void | DL_SYSCTL_enableSleepOnExit (void) |

| Enable sleep on exit. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableSleepOnExit (void) |

| Disable sleep on exit. More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isSleepOnExitEnabled (void) |

| Check if sleep on exit is enabled. | |

| __STATIC_INLINE void | DL_SYSCTL_enableEventOnPend (void) |

| Enable send event on pending bit. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableEventOnPend (void) |

| Disable send event on pending bit. More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isEventOnPendEnabled (void) |

| Check if send event on pending bit is enabled. More... | |

| void | DL_SYSCTL_switchMCLKfromSYSOSCtoLFCLK (bool disableSYSOSC) |

| Change MCLK source from SYSOSC to LFCLK. More... | |

| void | DL_SYSCTL_switchMCLKfromLFCLKtoSYSOSC (void) |

| Change MCLK source from LFCLK to SYSOSC. More... | |

| void | DL_SYSCTL_switchMCLKfromSYSOSCtoHSCLK (void) |

| Change MCLK source from SYSOSC to HSCLK. More... | |

| void | DL_SYSCTL_switchMCLKfromHSCLKtoSYSOSC (void) |

| Change MCLK source from HSCLK to SYSOSC. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicyRUN0SLEEP0 (void) |

| Set the RUN/SLEEP mode power policy to RUN0/SLEEP0. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicyRUN1SLEEP1 (void) |

| Set the RUN/SLEEP mode power policy to RUN1/SLEEP1. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicyRUN2SLEEP2 (void) |

| Set the RUN/SLEEP mode power policy to RUN2/SLEEP2. More... | |

| DL_SYSCTL_POWER_POLICY_RUN_SLEEP | DL_SYSCTL_getPowerPolicyRUNSLEEP (void) |

| Get the RUN/SLEEP mode power policy. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicySTOP0 (void) |

| Set the STOP mode power policy to STOP0. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicySTOP2 (void) |

| Set the STOP mode power policy to STOP2. More... | |

| DL_SYSCTL_POWER_POLICY_STOP | DL_SYSCTL_getPowerPolicySTOP (void) |

| Get the STOP mode power policy. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicySTANDBY0 (void) |

| Set the STANDBY mode power policy to STANDBY0. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicySTANDBY1 (void) |

| Set the STANDBY mode power policy to STANDBY1. More... | |

| DL_SYSCTL_POWER_POLICY_STANDBY | DL_SYSCTL_getPowerPolicySTANDBY (void) |

| Get the STANDBY mode power policy. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setPowerPolicySHUTDOWN (void) |

| Set power policy to SHUTDOWN mode. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setBORThreshold (DL_SYSCTL_BOR_THRESHOLD_LEVEL thresholdLevel) |

| Set the brown-out reset (BOR) threshold level. More... | |

| __STATIC_INLINE DL_SYSCTL_BOR_THRESHOLD_LEVEL | DL_SYSCTL_getBORThreshold (void) |

| Get the brown-out reset (BOR) threshold level. More... | |

| __STATIC_INLINE void | DL_SYSCTL_activateBORThreshold (void) |

| Activate the BOR threshold level. More... | |

| __STATIC_INLINE void | DL_SYSCTL_resetDevice (uint32_t resetType) |

| Resets the device. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableInterrupt (uint32_t interruptMask) |

| Enable SYSCTL interrupts. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableInterrupt (uint32_t interruptMask) |

| Disable SYSCTL interrupts. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getEnabledInterrupts (uint32_t interruptMask) |

| Check which SYSCTL interrupts are enabled. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getEnabledInterruptStatus (uint32_t interruptMask) |

| Check interrupt flag of enabled SYSCTL interrupts. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getRawInterruptStatus (uint32_t interruptMask) |

| Check interrupt flag of any SYSCTL interrupt. More... | |

| __STATIC_INLINE DL_SYSCTL_IIDX | DL_SYSCTL_getPendingInterrupt (void) |

| Get highest priority pending SYSCTL interrupt. More... | |

| __STATIC_INLINE void | DL_SYSCTL_clearInterruptStatus (uint32_t interruptMask) |

| Clear pending SYSCTL interrupts. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getRawNonMaskableInterruptStatus (uint32_t interruptMask) |

| Check interrupt flag of any SYSCTL non-maskable interrupt. More... | |

| __STATIC_INLINE DL_SYSCTL_NMI_IIDX | DL_SYSCTL_getPendingNonMaskableInterrupt (void) |

| Get highest priority pending SYSCTL non-maskable interrupt. More... | |

| __STATIC_INLINE void | DL_SYSCTL_clearNonMaskableInterruptStatus (uint32_t interruptMask) |

| Clear pending SYSCTL non-maskable interrupts. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setWWDT0ErrorBehavior (DL_SYSCTL_ERROR_BEHAVIOR behavior) |

| Set the behavior when a WWDT0 error occurs. More... | |

| __STATIC_INLINE DL_SYSCTL_ERROR_BEHAVIOR | DL_SYSCTL_getWWDT0ErrorBehavior (void) |

| Get the behavior when a WWDT0 error occurs. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setMCLKDivider (DL_SYSCTL_MCLK_DIVIDER divider) |

| Set the Main Clock (MCLK) divider (MDIV) More... | |

| __STATIC_INLINE DL_SYSCTL_MCLK_DIVIDER | DL_SYSCTL_getMCLKDivider (void) |

| Get the Main Clock (MCLK) divider (MDIV) More... | |

| __STATIC_INLINE DL_SYSCTL_MCLK_SOURCE | DL_SYSCTL_getMCLKSource (void) |

| Get the source for the Main Clock (MCLK) More... | |

| __STATIC_INLINE void | DL_SYSCTL_setSYSOSCFreq (DL_SYSCTL_SYSOSC_FREQ freq) |

| Set the target frequency of the System Oscillator (SYSOSC) More... | |

| __STATIC_INLINE DL_SYSCTL_SYSOSC_FREQ | DL_SYSCTL_getTargetSYSOSCFreq (void) |

| Get the target frequency of the System Oscillator (SYSOSC) Target/desired SYSOSC frequency may be different than current/actual SYSOSC frequency during gear shift and other operations. This function matches what is input by DL_SYSCTL_setSYSOSCFreq. More... | |

| __STATIC_INLINE DL_SYSCTL_SYSOSC_FREQ | DL_SYSCTL_getCurrentSYSOSCFreq (void) |

| Get the current frequency of the System Oscillator (SYSOSC) Current/actual SYSOSC frequency may be different than target/desired SYSOSC frequency during gear shift and other operations. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getClockStatus (void) |

| Returns status of the different clocks in CKM. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getStatus (void) |

| Returns general status of SYSCTL. More... | |

| __STATIC_INLINE void | DL_SYSCTL_clearECCErrorStatus (void) |

| Clear the ECC error bits in SYSSTATUS. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setLFCLKSourceEXLF (void) |

| Change LFCLK source to external digital LFCLK_IN. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setHFCLKSourceHFCLKIN (void) |

| Change HFCLK source to external digital HFCLK_IN. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableMFCLK (void) |

| Enable the Medium Frequency Clock (MFCLK) More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableMFCLK (void) |

| Disable the Medium Frequency Clock (MFCLK) | |

| __STATIC_INLINE void | DL_SYSCTL_enableExternalClock (DL_SYSCTL_CLK_OUT_SOURCE source, DL_SYSCTL_CLK_OUT_DIVIDE divider) |

| Enable the External Clock (CLK_OUT) More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableExternalClock (void) |

| Disable the External Clock (CLK_OUT) More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableExternalClockDivider (void) |

| Disable the External Clock (CLK_OUT) Divider. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableMFPCLK (void) |

| Enable the Middle Frequency Precision Clock (MFPCLK) More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableMFPCLK (void) |

| Disable the Middle Frequency Precision Clock (MFPCLK) More... | |

| __STATIC_INLINE void | DL_SYSCTL_blockAllAsyncFastClockRequests (void) |

| Blocks all asynchronous fast clock requests. More... | |

| __STATIC_INLINE void | DL_SYSCTL_allowAllAsyncFastClockRequests (void) |

| Allows all asynchronous fast clock requests. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableFastCPUEventHandling (void) |

| Generates an asynchronous fast clock request upon any IRQ request to CPU. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableFastCPUEventHandling (void) |

| Maintains current system clock speed for IRQ request to CPU. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setSRAMBoundaryAddress (uint32_t address) |

| Set the SRAM boundary address to act as partition for read-execute permission. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getSRAMBoundaryAddress (void) |

| Get the SRAM boundary address. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_readFCC (void) |

| Read Frequency Clock Counter (FCC) More... | |

| __STATIC_INLINE void | DL_SYSCTL_startFCC (void) |

| Start Frequency Clock Counter (FCC) More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isFCCDone (void) |

| Returns whether FCC is done capturing. More... | |

| void | DL_SYSCTL_configFCC (DL_SYSCTL_FCC_TRIG_TYPE trigLvl, DL_SYSCTL_FCC_TRIG_SOURCE trigSrc, DL_SYSCTL_FCC_CLOCK_SOURCE clkSrc) |

| Configure the Frequency Clock Counter (FCC) More... | |

| __STATIC_INLINE void | DL_SYSCTL_setFCCPeriods (DL_SYSCTL_FCC_TRIG_CNT periods) |

| Sets number of rising-edge to rising-edge period for Frequency Clock Counter (FCC) More... | |

| __STATIC_INLINE DL_SYSCTL_FCC_TRIG_CNT | DL_SYSCTL_getFCCPeriods (void) |

| Gets number of rising-edge to rising-edge period for Frequency Clock Counter (FCC) More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableSYSOSCFCL (void) |

| Enable Frequency Correction Loop (FCL) in Internal Resistor mode. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableWriteLock (void) |

| Enable write protection of selected SYSCTL registers. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableWriteLock (void) |

| Disable write protection of selected SYSCTL registers. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setVBOOSTConfig (DL_SYSCTL_VBOOST setting) |

| Sets operating mode of VBOOST (analog charge pump) More... | |

| __STATIC_INLINE DL_SYSCTL_VBOOST | DL_SYSCTL_getVBOOSTConfig (void) |

| Gets operating mode of VBOOST (analog charge pump) More... | |

| __STATIC_INLINE uint8_t | DL_SYSCTL_getShutdownStorageByte (DL_SYSCTL_SHUTDOWN_STORAGE_BYTE index) |

| Return byte that was saved through SHUTDOWN. More... | |

| __STATIC_INLINE void | DL_SYSCTL_setShutdownStorageByte (DL_SYSCTL_SHUTDOWN_STORAGE_BYTE index, uint8_t data) |

| Save a byte to SHUTDOWN memory. More... | |

| __STATIC_INLINE void | DL_SYSCTL_releaseShutdownIO (void) |

| Enable SHUTDOWN IO Release. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableNRSTPin (void) |

| Disable the reset functionality of the NRST pin. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableSWD (void) |

| Disable Serial Wire Debug (SWD) functionality. More... | |

| __STATIC_INLINE DL_SYSCTL_RESET_CAUSE | DL_SYSCTL_getResetCause (void) |

| Return byte that is stored in RSTCAUSE. More... | |

| __STATIC_INLINE uint32_t | DL_SYSCTL_getTempCalibrationConstant (void) |

| Retrieves the calibration constant of the temperature sensor to be used in temperature calculation. More... | |

| __STATIC_INLINE void | DL_SYSCTL_enableBeeperOutput (void) |

| Enable Beeper output. More... | |

| __STATIC_INLINE void | DL_SYSCTL_disableBeeperOutput (void) |

| Disable Beeper output. | |

| __STATIC_INLINE void | DL_SYSCTL_setBeeperFreq (DL_SYSCTL_BEEPER_FREQ freq) |

| Set the target frequency of the Beeper output. More... | |

| __STATIC_INLINE DL_SYSCTL_BEEPER_FREQ | DL_SYSCTL_getBeeperFreq (void) |

| Get the target frequency of the the Beeper output. More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isBeeperEnabled (void) |

| Check if Beeper is enabled. More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isFlashBankSwapEnabled (void) |

| Checks if Flash Bank swapping is enabled. More... | |

| __STATIC_INLINE bool | DL_SYSCTL_isExecuteFromUpperFlashBank (void) |

| Checks if executing from upper flash bank. More... | |

The System Control (SysCtl) module enables control over system wide settings like clocks and power management.

| #define DL_SYSCTL_setMCLKSource | ( | current, | |

| next, | |||

| ... | |||

| ) | DL_SYSCTL_switchMCLKfrom##current##to##next(__VA_ARGS__); |

Change MCLK source.

To ensure good clocking behavior, these are the recommended steps for transition. Valid sources and destinations: LFCLK, SYSOSC, HSCLK

Depending on current MCLK source, steps to switch to next MCLK source can vary. This is a macro that redirects to the different possible transitions.

Only valid for RUN modes. In low power modes, MCLK transitions are handled by hardware.

Referenced by DL_SYSCTL_setPowerPolicyRUN0SLEEP0(), DL_SYSCTL_setPowerPolicyRUN1SLEEP1(), and DL_SYSCTL_setPowerPolicyRUN2SLEEP2().

| enum DL_SYSCTL_IIDX |

| enum DL_SYSCTL_NMI_IIDX |

| Enumerator | |

|---|---|

| DL_SYSCTL_CLK_OUT_SOURCE_SYSOSC | Use System Oscillator (SYSOSC) as CLK_OUT source |

| DL_SYSCTL_CLK_OUT_SOURCE_ULPCLK | Use Ultra Low Power Clock (ULPCLK) as CLK_OUT source. DL_SYSCTL_CLK_OUT_DIVIDE_DISABLE must not be selected for this configuration. |

| DL_SYSCTL_CLK_OUT_SOURCE_LFCLK | Use Low Frequency Clock (LFCLK) as CLK_OUT source |

| DL_SYSCTL_CLK_OUT_SOURCE_MFPCLK | Use Middle Frequency Precision Clock (MFPCLK) as CLK_OUT source. DL_SYSCTL_CLK_OUT_DIVIDE_DISABLE must not be selected for this configuration. |

| DL_SYSCTL_CLK_OUT_SOURCE_HFCLK | Use High Frequency Clock (HFCLK) as CLK_OUT source |

| enum DL_SYSCTL_VBOOST |

| __STATIC_INLINE void DL_SYSCTL_enableSleepOnExit | ( | void | ) |

Enable sleep on exit.

Enables sleep on exit when the CPU moves from handler mode to thread mode. By enabling, allows an interrupt driven application to avoid returning to an empty main application.

| __STATIC_INLINE void DL_SYSCTL_disableSleepOnExit | ( | void | ) |

Disable sleep on exit.

Disables sleep on exit when the CPU moves from handler mode to thread mode.

| __STATIC_INLINE void DL_SYSCTL_enableEventOnPend | ( | void | ) |

Enable send event on pending bit.

When enabled, any enabled event and all interrupts (including disabled interrupts) can wakeup the processor.

| __STATIC_INLINE void DL_SYSCTL_disableEventOnPend | ( | void | ) |

Disable send event on pending bit.

When disabled, only enabled interrupts or events can wake up the processor. Disabled interrupts are excluded.

| __STATIC_INLINE bool DL_SYSCTL_isEventOnPendEnabled | ( | void | ) |

Check if send event on pending bit is enabled.

| true | Send event on pending bit is enabled |

| false | Send event on pending bit is disabled |

| void DL_SYSCTL_switchMCLKfromSYSOSCtoLFCLK | ( | bool | disableSYSOSC | ) |

Change MCLK source from SYSOSC to LFCLK.

| [in] | disableSYSOSC | Whether to leave SYSOSC running or not |

| void DL_SYSCTL_switchMCLKfromLFCLKtoSYSOSC | ( | void | ) |

Change MCLK source from LFCLK to SYSOSC.

| void DL_SYSCTL_switchMCLKfromSYSOSCtoHSCLK | ( | void | ) |

Change MCLK source from SYSOSC to HSCLK.

| void DL_SYSCTL_switchMCLKfromHSCLKtoSYSOSC | ( | void | ) |

Change MCLK source from HSCLK to SYSOSC.

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicyRUN0SLEEP0 | ( | void | ) |

Set the RUN/SLEEP mode power policy to RUN0/SLEEP0.

In RUN0, the MCLK and the CPUCLK run from a fast clock source (SYSOSC, HFCLK, or SYSPLL).

Setting the RUN power policy will also set the SLEEP power policy. The SLEEP mode behavior is always identical to RUN mode, just with the CPUCLK disabled. As such, the SLEEP behavior is determined by the configuration of the RUN mode. To actually enter SLEEP mode, you must call __WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application.

There are three RUN/SLEEP mode policy options: RUN0/SLEEP0, RUN1/SLEEP1, and RUN2/SLEEP2. Refer to the device TRM for more information on each policy

References DL_SYSCTL_setMCLKSource.

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicyRUN1SLEEP1 | ( | void | ) |

Set the RUN/SLEEP mode power policy to RUN1/SLEEP1.

In RUN1, the MCLK and the CPUCLK run from LFCLK (at 32kHz) to reduce active power, but SYSOSC is left enabled to service analog modules such as an ADC, DAC, OPA, or COMP (in HS mode).

Setting the RUN power policy will also set the SLEEP power policy. The SLEEP mode behavior is always identical to RUN mode, just with the CPUCLK disabled. As such, the SLEEP behavior is determined by the configuration of the RUN mode. To actually enter SLEEP mode, you must call __WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application.

There are three RUN/SLEEP mode policy options: RUN0/SLEEP0, RUN1/SLEEP1, and RUN2/SLEEP2. Refer to the device TRM for more information on each policy

References DL_SYSCTL_setMCLKSource.

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicyRUN2SLEEP2 | ( | void | ) |

Set the RUN/SLEEP mode power policy to RUN2/SLEEP2.

In RUN2, the MCLK and the CPUCLK run from LFCLK (at 32kHz), and SYSOSC is completely disabled to save power. This is the lowest power state with the CPU running

Setting the RUN power policy will also set the SLEEP power policy. The SLEEP mode behavior is always identical to RUN mode, just with the CPUCLK disabled. As such, the SLEEP behavior is determined by the configuration of the RUN mode. To actually enter SLEEP mode, you must call __WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application.

There are three RUN/SLEEP mode policy options: RUN0/SLEEP0, RUN1/SLEEP1, and RUN2/SLEEP2. Refer to the device TRM for more information on each policy

References DL_SYSCTL_getPowerPolicyRUNSLEEP(), and DL_SYSCTL_setMCLKSource.

| DL_SYSCTL_POWER_POLICY_RUN_SLEEP DL_SYSCTL_getPowerPolicyRUNSLEEP | ( | void | ) |

Get the RUN/SLEEP mode power policy.

Get which RUN/SLEEP power policy has been set.

The SLEEP mode behavior is always identical to RUN mode, just with the CPUCLK disabled. As such, the SLEEP behavior is determined by the configuration of the RUN mode.

| One | of DL_SYSCTL_POWER_POLICY_RUN_SLEEP |

Referenced by DL_SYSCTL_setPowerPolicyRUN2SLEEP2().

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicySTOP0 | ( | void | ) |

Set the STOP mode power policy to STOP0.

In STOP0, the SYSOSC is left running at the current frequency when entering STOP mode (either 32MHz, 24MHz, 16MHz, or 4MHz). ULPCLK is always limited to 4MHz automatically by hardware, but SYSOSC is not disturbed to support consistent operation of analog peripherals such as the ADC, OPA, or COMP.

There are two STOP mode policy options: STOP0 and STOP2. STOP0 should only be entered from RUN0 or SLEEP0. Refer to the device TRM for more information on each policy.

__WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application. | __STATIC_INLINE void DL_SYSCTL_setPowerPolicySTOP2 | ( | void | ) |

Set the STOP mode power policy to STOP2.

In STOP2, the SYSOSC is disabled and the ULPCLK is sourced from LFCLK at 32kHz. This is the lowest power state in STOP mode.

There are two STOP mode policy options: STOP0 and STOP2. STOP2 should only be entered from RUN2 or SLEEP2. Refer to the device TRM for more information on each policy.

__WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application. References DL_SYSCTL_getPowerPolicySTOP().

| DL_SYSCTL_POWER_POLICY_STOP DL_SYSCTL_getPowerPolicySTOP | ( | void | ) |

Get the STOP mode power policy.

Get which STOP power policy has been set.

| One | of DL_SYSCTL_POWER_POLICY_STOP if a STOP power policy |

Referenced by DL_SYSCTL_setPowerPolicySTOP2().

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicySTANDBY0 | ( | void | ) |

Set the STANDBY mode power policy to STANDBY0.

In STANDBY0, all PD0 peripherals receive the ULPCLK and LFCLK, and the RTC receives RTCCLK.

There are two STANDBY mode policy options: STANDBY0 and STANDBY1.

__WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application. | __STATIC_INLINE void DL_SYSCTL_setPowerPolicySTANDBY1 | ( | void | ) |

Set the STANDBY mode power policy to STANDBY1.

In STANDBY1, only TIMG0 and TIMG1 receive ULPCLK/LFCLK. The RTC continues to receive RTCCLK. A TIMG0/1 interrupt, RTC interrupt, or ADC trigger in STANDBY1 always triggers an asynchronous fast clock request to wake the system. Other PD0 peripherals (such as UART, I2C, GPIO, and COMP) can also wake the system upon an external event through an asynchronous fast clock request, but they are not actively clocked in STANDBY1.

There are two STANDBY mode policy options: STANDBY0 and STANDBY1.

__WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application. References DL_SYSCTL_getPowerPolicySTANDBY().

| DL_SYSCTL_POWER_POLICY_STANDBY DL_SYSCTL_getPowerPolicySTANDBY | ( | void | ) |

Get the STANDBY mode power policy.

Get which STANDBY power policy has been set.

| One | of DL_SYSCTL_POWER_POLICY_STANDBY |

Referenced by DL_SYSCTL_setPowerPolicySTANDBY1().

| __STATIC_INLINE void DL_SYSCTL_setPowerPolicySHUTDOWN | ( | void | ) |

Set power policy to SHUTDOWN mode.

In SHUTDOWN mode, no clocks are available. The core regulator is completely disabled and all SRAM and register contents are lost, with the exception of the 4 bytes of general purpose memory in SYSCTL which may be used to store state information. The BOR and bandgap circuit are disabled. The device may wake up via a wake-up capable IO, a debug connection, or NRST. SHUTDOWN mode has the lowest current consumption of any operating mode. Exiting SHUTDOWN mode triggers a BOR.

There is only one SHUTDOWN mode policy option: SHUTDOWN.

__WFI() to wait for interrupts or __WFE() to wait for ARM events. __WFI() is used in interrupt-driven applications, and __WFE() is used for interactions between the interrupt handler and main application. | __STATIC_INLINE void DL_SYSCTL_setBORThreshold | ( | DL_SYSCTL_BOR_THRESHOLD_LEVEL | thresholdLevel | ) |

Set the brown-out reset (BOR) threshold level.

Note that this API does NOT activate the BOR threshold. After setting the threshold level with this API, call DL_SYSCTL_activateBORThreshold to actually activate the new threshold.

During startup, the BOR threshold defaults to BOR0 (the lowet value) to ensure the device always starts at the specified VDD minimum. After boot, the BOR threshold level can be configured to a different level. When the BOR threshold is BOR0, a BOR0- violation always generates a BOR- violation signal to SYSCTL, generating a BOR level reset. When the BOR threshold is re-configured to BOR1, BOR2, or BOR3 the BOR circuit will generate a SYSCTL interrupt rather than asserting a BOR- violation. This may be used to give the application an indication that the supply has dropped below a certain level without causing a reset. If the BOR is in interrupt mode (threshold level of BOR1-3), and VDD drops below the respective BORx- level, an interrupt will be generated and the BOR circuit will automatically switch the BOR threshold level to BOR0 to ensure that a BOR- violation is asserted if VDD drops below BOR0-.

| [in] | thresholdLevel | The BOR threshold level to set. One of DL_SYSCTL_BOR_THRESHOLD_LEVEL. |

| __STATIC_INLINE DL_SYSCTL_BOR_THRESHOLD_LEVEL DL_SYSCTL_getBORThreshold | ( | void | ) |

Get the brown-out reset (BOR) threshold level.

| One | of DL_SYSCTL_BOR_THRESHOLD_LEVEL |

| __STATIC_INLINE void DL_SYSCTL_activateBORThreshold | ( | void | ) |

Activate the BOR threshold level.

Attempts to change the active BOR mode to the BOR threshold that was set via DL_SYSCTL_setBORThreshold.

Setting this bit also clears any prior BOR violation status indications.

After calling this API, the change can be validated by calling DL_SYSCTL_getStatus and checking the return value.

| __STATIC_INLINE void DL_SYSCTL_resetDevice | ( | uint32_t | resetType | ) |

Resets the device.

Resets the device using the type of reset selected. This function does not return, the reset will happen immediately.

| [in] | resetType | Type of reset to perform. One of DL_SYSCTL_RESET. |

| __STATIC_INLINE void DL_SYSCTL_enableInterrupt | ( | uint32_t | interruptMask | ) |

Enable SYSCTL interrupts.

| [in] | interruptMask | Bit mask of interrupts to enable. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| __STATIC_INLINE void DL_SYSCTL_disableInterrupt | ( | uint32_t | interruptMask | ) |

Disable SYSCTL interrupts.

| [in] | interruptMask | Bit mask of interrupts to enable. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| __STATIC_INLINE uint32_t DL_SYSCTL_getEnabledInterrupts | ( | uint32_t | interruptMask | ) |

Check which SYSCTL interrupts are enabled.

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| Bitwise | OR of DL_SYSCTL_INTERRUPT values |

| __STATIC_INLINE uint32_t DL_SYSCTL_getEnabledInterruptStatus | ( | uint32_t | interruptMask | ) |

Check interrupt flag of enabled SYSCTL interrupts.

Checks if any of the SYSCTL interrupts that were previously enabled are pending.

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| Bitwise | OR of DL_SYSCTL_INTERRUPT values |

| __STATIC_INLINE uint32_t DL_SYSCTL_getRawInterruptStatus | ( | uint32_t | interruptMask | ) |

Check interrupt flag of any SYSCTL interrupt.

Checks if any of the SYSCTL interrupts are pending. Interrupts do not have to be previously enabled.

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| Bitwise | OR of DL_SYSCTL_INTERRUPT values |

| __STATIC_INLINE DL_SYSCTL_IIDX DL_SYSCTL_getPendingInterrupt | ( | void | ) |

Get highest priority pending SYSCTL interrupt.

Checks if any of the SYSCTL interrupts are pending. Interrupts do not have to be previously enabled.

| One | of DL_SYSCTL_IIDX values |

| __STATIC_INLINE void DL_SYSCTL_clearInterruptStatus | ( | uint32_t | interruptMask | ) |

Clear pending SYSCTL interrupts.

| [in] | interruptMask | Bit mask of interrupts to clear. Bitwise OR of DL_SYSCTL_INTERRUPT. |

| __STATIC_INLINE uint32_t DL_SYSCTL_getRawNonMaskableInterruptStatus | ( | uint32_t | interruptMask | ) |

Check interrupt flag of any SYSCTL non-maskable interrupt.

Checks if any of the SYSCTL non-maskable interrupts are pending. Interrupts do not have to be previously enabled.

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SYSCTL_NMI. |

| Bitwise | OR of DL_SYSCTL_NMI values |

| __STATIC_INLINE DL_SYSCTL_NMI_IIDX DL_SYSCTL_getPendingNonMaskableInterrupt | ( | void | ) |

Get highest priority pending SYSCTL non-maskable interrupt.

Checks if any of the SYSCTL non-maskable interrupts are pending. Interrupts do not have to be previously enabled.

| One | of DL_SYSCTL_NMI_IIDX values |

| __STATIC_INLINE void DL_SYSCTL_clearNonMaskableInterruptStatus | ( | uint32_t | interruptMask | ) |

Clear pending SYSCTL non-maskable interrupts.

| [in] | interruptMask | Bit mask of interrupts to clear. Bitwise OR of DL_SYSCTL_NMI. |

| __STATIC_INLINE void DL_SYSCTL_setWWDT0ErrorBehavior | ( | DL_SYSCTL_ERROR_BEHAVIOR | behavior | ) |

Set the behavior when a WWDT0 error occurs.

Configures whether a WWDT0 error will trigger a BOOTRST or an NMI (non-maskable interrupt). By default, this error will trigger a BOOTRST.

| [in] | behavior | The behavior when a Flash ECC DED occurrs |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_ERROR_BEHAVIOR DL_SYSCTL_getWWDT0ErrorBehavior | ( | void | ) |

Get the behavior when a WWDT0 error occurs.

By default, this error will trigger a BOOTRST.

| One | of DL_SYSCTL_ERROR_BEHAVIOR |

| __STATIC_INLINE void DL_SYSCTL_setMCLKDivider | ( | DL_SYSCTL_MCLK_DIVIDER | divider | ) |

Set the Main Clock (MCLK) divider (MDIV)

Additionally, can use this function to disable MDIV. MDIV must be disabled before changing SYSOSC frequency.

MDIV is not valid if MCLK source is HSCLK. MDIV is not used if MCLK source if LFCLK.

| [in] | divider | Should be DL_SYSCTL_MCLK_DIVIDER_DISABLE if source is HSCLK, a don't care if LFCLK, and one of DL_SYSCTL_MCLK_DIVIDER if SYSOSC. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_MCLK_DIVIDER DL_SYSCTL_getMCLKDivider | ( | void | ) |

Get the Main Clock (MCLK) divider (MDIV)

| Should | be DL_SYSCTL_MCLK_DIVIDER_DISABLE if source is HSCLK, a don't care if LFCLK, and one of DL_SYSCTL_MCLK_DIVIDER if SYSOSC. |

| __STATIC_INLINE DL_SYSCTL_MCLK_SOURCE DL_SYSCTL_getMCLKSource | ( | void | ) |

Get the source for the Main Clock (MCLK)

| One | of DL_SYSCTL_MCLK_SOURCE |

| __STATIC_INLINE void DL_SYSCTL_setSYSOSCFreq | ( | DL_SYSCTL_SYSOSC_FREQ | freq | ) |

Set the target frequency of the System Oscillator (SYSOSC)

Target/desired SYSOSC frequency may be different than current/actual SYSOSC frequency during gear shift and other operations.

The System Oscillator (SYSOSC) is an on-chip, accurate, configurable oscillator with factory trimmed support for 32MHz (base frequency) and 4MHz (low frequency) operation.

SYSOSC provides a flexible high-speed clock source for the system in cases where the HFXT is either not present or not used.

MDIV must be disabled before changing SYSOSC freq. See DL_SYSCTL_setMCLKDivider.

| [in] | freq | Target frequency to use for the System Oscillator (SYSOSC). DL_SYSCTL_SYSOSC_FREQ_4M or DL_SYSCTL_SYSOSC_FREQ_BASE. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_SYSOSC_FREQ DL_SYSCTL_getTargetSYSOSCFreq | ( | void | ) |

Get the target frequency of the System Oscillator (SYSOSC) Target/desired SYSOSC frequency may be different than current/actual SYSOSC frequency during gear shift and other operations. This function matches what is input by DL_SYSCTL_setSYSOSCFreq.

| __STATIC_INLINE DL_SYSCTL_SYSOSC_FREQ DL_SYSCTL_getCurrentSYSOSCFreq | ( | void | ) |

Get the current frequency of the System Oscillator (SYSOSC) Current/actual SYSOSC frequency may be different than target/desired SYSOSC frequency during gear shift and other operations.

| __STATIC_INLINE uint32_t DL_SYSCTL_getClockStatus | ( | void | ) |

Returns status of the different clocks in CKM.

| Bitwise | OR of DL_SYSCTL_CLK_STATUS. |

Referenced by DL_SYSCTL_isFCCDone().

| __STATIC_INLINE uint32_t DL_SYSCTL_getStatus | ( | void | ) |

Returns general status of SYSCTL.

| Bitwise | OR of DL_SYSCTL_STATUS. |

| __STATIC_INLINE void DL_SYSCTL_clearECCErrorStatus | ( | void | ) |

Clear the ECC error bits in SYSSTATUS.

The ECC error bits in SYSSTATUS are sticky (they remain set when an ECC error occurs even if future reads do not have errors), and can be cleared through this API.

| __STATIC_INLINE void DL_SYSCTL_setLFCLKSourceEXLF | ( | void | ) |

Change LFCLK source to external digital LFCLK_IN.

LFOSC is the internal 32kHz oscillator and default LFCLK source after a BOR. Once LFCLK source is changed, the change is locked, LFOSC is disabled to save power, and LFCLK source cannot be selected again without BOR.

LFCLK_IN is a low frequency digital clock input compatible with 32.768kHz typical frequency digital square wave CMOS clock inputs (typical duty cycle of 50%).

Digital clock input must be valid and GPIO/IOMUX must be configured separately on the appropriate pin before calling this function to enable LFCLK_IN.

LFCLK_IN and LFXT are mutually exclusive. This function assumes LFXT is disabled (default).

| __STATIC_INLINE void DL_SYSCTL_setHFCLKSourceHFCLKIN | ( | void | ) |

Change HFCLK source to external digital HFCLK_IN.

HFCLK_IN can be used to bypass the HFXT circuit and bring 4-48MHz typical frequency digital clock into the devce as HFCLK source instead of HFXT.

HFCLK_IN is a digital clock input compatible with digital square wave CMOS clock inputs and should have typical duty cycle of 50%.

Digital clock input must be valid and GPIO/IOMUX must be configured separately on the appropriate pin before calling this function to enable HFCLK_IN.

| __STATIC_INLINE void DL_SYSCTL_enableMFCLK | ( | void | ) |

Enable the Medium Frequency Clock (MFCLK)

MFCLK provides a continuous 4MHz clock to drive certain peripherals on the system. The 4MHz rate is always derived from SYSOSC, and the divider is automatically applied to maintain the 4MHz rate regardless of SYSOSC frequency. MCLK is ideal for timers and serial interfaces which require a constant clock source in RUN/SLEEP/STOP power modes.

MFCLK can only run if 3 conditions are met:

1) Power mode must be RUN, SLEEP, or STOP. 2) USEMFTICK register bit is set, which this function does 3) MDIV must be set to DL_SYSCTL_MCLK_DIVIDER_DISABLE by DL_SYSCTL_setMCLKDivider.

If MCLK source is not SYSOSC, MCLK frequency must be >=32MHz for correct operation of MFCLK.

| __STATIC_INLINE void DL_SYSCTL_enableExternalClock | ( | DL_SYSCTL_CLK_OUT_SOURCE | source, |

| DL_SYSCTL_CLK_OUT_DIVIDE | divider | ||

| ) |

Enable the External Clock (CLK_OUT)

CLK_OUT is provided for pushing out digital clocks to external circuits, such as an external ADC which does not have its own clock source.

IOMUX setting for CLK_OUT must be configured before using this function.

CLK_OUT has a typical duty cycle of 50% if clock source is HFCLK, SYSPLLOUT1, SYSOSC, or LFCLK. If source is MCLK, ULPCLK, or MFCLK, duty cycle is not guaranteed to be 50%.

This function performs multiple operations: 1) Sets the CLK_OUT source 2) Sets the CLK_OUT divider value 3) Enables the CLK_OUT divider, which can be disabled by DL_SYSCTL_disableExternalClockDivider 4) Enables the CLK_OUT, which can be disabled by DL_SYSCTL_disableExternalClock

| [in] | source | The source of CLK_OUT. One of DL_SYSCTL_CLK_OUT_SOURCE. |

| [in] | divider | The divider of CLK_OUT. One of DL_SYSCTL_CLK_OUT_DIVIDE. |

References DL_Common_updateReg().

| __STATIC_INLINE void DL_SYSCTL_disableExternalClock | ( | void | ) |

Disable the External Clock (CLK_OUT)

| __STATIC_INLINE void DL_SYSCTL_disableExternalClockDivider | ( | void | ) |

Disable the External Clock (CLK_OUT) Divider.

| __STATIC_INLINE void DL_SYSCTL_enableMFPCLK | ( | void | ) |

Enable the Middle Frequency Precision Clock (MFPCLK)

MFPCLK provides a continuous fixed 4MHz clock to some analog peripherals.

| __STATIC_INLINE void DL_SYSCTL_disableMFPCLK | ( | void | ) |

Disable the Middle Frequency Precision Clock (MFPCLK)

| __STATIC_INLINE void DL_SYSCTL_blockAllAsyncFastClockRequests | ( | void | ) |

Blocks all asynchronous fast clock requests.

To block specific async fast clock requests on certain IP, refer to their individual driverlib. Examples include: RTC, UART, SPI, I2C.

| __STATIC_INLINE void DL_SYSCTL_allowAllAsyncFastClockRequests | ( | void | ) |

Allows all asynchronous fast clock requests.

Although this allows all async fast clock requests, individual IPs may still be blocking theirs.

To allow specific async fast clock requests on certain IP, refer to their individual driverlib. Examples include: RTC, UART, SPI, I2C, GPIO.

| __STATIC_INLINE void DL_SYSCTL_enableFastCPUEventHandling | ( | void | ) |

Generates an asynchronous fast clock request upon any IRQ request to CPU.

Provides lowest latency interrupt handling regardless of system clock speed. Blockable by DL_SYSCTL_blockAllAsyncFastClockRequests

| __STATIC_INLINE void DL_SYSCTL_disableFastCPUEventHandling | ( | void | ) |

Maintains current system clock speed for IRQ request to CPU.

Latency for interrupt handling will be higher at lower system clock speeds.

| __STATIC_INLINE void DL_SYSCTL_setSRAMBoundaryAddress | ( | uint32_t | address | ) |

Set the SRAM boundary address to act as partition for read-execute permission.

Specify the SRAM partition address to protect the code region of SRAM from being written to, and prevent the RW ("data") region of SRAM from being used for code execution. The SRAM partition address creates lower and higher partitions:

The address is set with a 32-byte resolution. The address written is the system memory map address of the partition (0x200X_XXXX).

| [in] | address | Address to act as the SRAM partition address. Value is a valid 32-bit SRAM address. Only address bits [19:5] i.e. bit 5 to bit 19 are used for the boundary address |

| __STATIC_INLINE uint32_t DL_SYSCTL_getSRAMBoundaryAddress | ( | void | ) |

Get the SRAM boundary address.

Get the SRAM partition address The SRAM partition address creates lower and higher partitions:

The address is set with a 32-byte granularity. The address written is the system memory map address of the partition (0x200X_XXXX).

| Value | is range in [0x0, 0x000FFFE0] |

| __STATIC_INLINE uint32_t DL_SYSCTL_readFCC | ( | void | ) |

Read Frequency Clock Counter (FCC)

| __STATIC_INLINE void DL_SYSCTL_startFCC | ( | void | ) |

Start Frequency Clock Counter (FCC)

If FCC_IN is already logic high, counting starts immediately. When using level trigger, FCC_IN should be low when GO is set, and trigger pulse should be sent to FCC_IN after starting FCC.

| __STATIC_INLINE bool DL_SYSCTL_isFCCDone | ( | void | ) |

Returns whether FCC is done capturing.

When capture completes, FCCDONE is set by hardware. FCCDONE is read-only and is automatically cleared by hardware when a new capture is started.

| true | or false (boolean) |

References DL_SYSCTL_configFCC(), and DL_SYSCTL_getClockStatus().

| void DL_SYSCTL_configFCC | ( | DL_SYSCTL_FCC_TRIG_TYPE | trigLvl, |

| DL_SYSCTL_FCC_TRIG_SOURCE | trigSrc, | ||

| DL_SYSCTL_FCC_CLOCK_SOURCE | clkSrc | ||

| ) |

Configure the Frequency Clock Counter (FCC)

FCC enables flexible in-system testing and calibration of a variety of oscillators and clocks on the device. The FCC counts the number of clock periods seen on the selected clock source within a known fixed trigger period (derived from a secondary reference source) to provide an estimation of the frequency of the source clock.

| [in] | trigLvl | Determines if active high level trigger or rising-edge to rising-edge. One of DL_SYSCTL_FCC_TRIG_TYPE . |

| [in] | trigSrc | Determines which clock source to trigger FCC from. One of DL_SYSCTL_FCC_TRIG_SOURCE. |

| [in] | clkSrc | Which clock source to capture and measure frequency of. One of DL_SYSCTL_FCC_CLOCK_SOURCE. |

Referenced by DL_SYSCTL_isFCCDone().

| __STATIC_INLINE void DL_SYSCTL_setFCCPeriods | ( | DL_SYSCTL_FCC_TRIG_CNT | periods | ) |

Sets number of rising-edge to rising-edge period for Frequency Clock Counter (FCC)

Set the number of rising-edge to rising-edge period for Frequency Clock Counter (FCC)

| [in] | periods | One of DL_SYSCTL_FCC_TRIG_CNT |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_FCC_TRIG_CNT DL_SYSCTL_getFCCPeriods | ( | void | ) |

Gets number of rising-edge to rising-edge period for Frequency Clock Counter (FCC)

| __STATIC_INLINE void DL_SYSCTL_enableSYSOSCFCL | ( | void | ) |

Enable Frequency Correction Loop (FCL) in Internal Resistor mode.

Once FCL is enable, it cannot be disabled by software. A BOOTRST is required.

| __STATIC_INLINE void DL_SYSCTL_enableWriteLock | ( | void | ) |

Enable write protection of selected SYSCTL registers.

Protecting writes to configuration registers in SYSCTL can add a layer of robustness against unintended changes during runtime.

| __STATIC_INLINE void DL_SYSCTL_disableWriteLock | ( | void | ) |

Disable write protection of selected SYSCTL registers.

Protecting writes to configuration registers in SYSCTL can add a layer of robustness against unintended changes during runtime.

| __STATIC_INLINE void DL_SYSCTL_setVBOOSTConfig | ( | DL_SYSCTL_VBOOST | setting | ) |

Sets operating mode of VBOOST (analog charge pump)

Active VBOOST circuitry is needed for COMP/OPA/GPAMP (if present on device). VBOOST has a startup time, so consider power consumption versus desired startup time.

| [in] | setting | One of DL_SYSCTL_VBOOST. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_VBOOST DL_SYSCTL_getVBOOSTConfig | ( | void | ) |

Gets operating mode of VBOOST (analog charge pump)

Active VBOOST circuitry is needed for COMP/OPA/GPAMP (if present on device). VBOOST has a startup time, so consider power consumption versus desired startup time.

| __STATIC_INLINE uint8_t DL_SYSCTL_getShutdownStorageByte | ( | DL_SYSCTL_SHUTDOWN_STORAGE_BYTE | index | ) |

Return byte that was saved through SHUTDOWN.

Shutdown memory persists beyond BOR, BOOTRST, and SYSRST.

| [in] | index | One of DL_SYSCTL_SHUTDOWN_STORAGE_BYTE. |

| __STATIC_INLINE void DL_SYSCTL_setShutdownStorageByte | ( | DL_SYSCTL_SHUTDOWN_STORAGE_BYTE | index, |

| uint8_t | data | ||

| ) |

Save a byte to SHUTDOWN memory.

Shutdown memory persists beyond BOR, BOOTRST, and SYSRST.

| [in] | index | One of DL_SYSCTL_SHUTDOWN_STORAGE_BYTE. |

| [in] | data | 8-bit data to save in memory |

References DL_Common_updateReg().

| __STATIC_INLINE void DL_SYSCTL_releaseShutdownIO | ( | void | ) |

Enable SHUTDOWN IO Release.

After shutdown, IO is locked in previous state.

| __STATIC_INLINE void DL_SYSCTL_disableNRSTPin | ( | void | ) |

Disable the reset functionality of the NRST pin.

Disabling the NRST pin allows the pin to be configured as a GPIO. Once disabled, the reset functionality can only be re-enabled by a POR.

| __STATIC_INLINE void DL_SYSCTL_disableSWD | ( | void | ) |

Disable Serial Wire Debug (SWD) functionality.

SWD pins are enabled by default after cold start to allow a debug connection. It is possible to disable SWD on these pins to use for other functionality.

| __STATIC_INLINE DL_SYSCTL_RESET_CAUSE DL_SYSCTL_getResetCause | ( | void | ) |

Return byte that is stored in RSTCAUSE.

| __STATIC_INLINE uint32_t DL_SYSCTL_getTempCalibrationConstant | ( | void | ) |

Retrieves the calibration constant of the temperature sensor to be used in temperature calculation.

| Temperature | sensor calibration data |

References DL_FactoryRegion_getTemperatureVoltage().

| __STATIC_INLINE void DL_SYSCTL_enableBeeperOutput | ( | void | ) |

Enable Beeper output.

The Beeper function can be used to generate a square wave output to external beepers. The frequency of the Beeper output can be configued by calling DL_SYSCTL_setBeeperFreq

| __STATIC_INLINE void DL_SYSCTL_setBeeperFreq | ( | DL_SYSCTL_BEEPER_FREQ | freq | ) |

Set the target frequency of the Beeper output.

| [in] | freq | Target frequency to use for the Beeper output. One of DL_SYSCTL_BEEPER_FREQ. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SYSCTL_BEEPER_FREQ DL_SYSCTL_getBeeperFreq | ( | void | ) |

Get the target frequency of the the Beeper output.

| One | of DL_SYSCTL_BEEPER_FREQ. |

| __STATIC_INLINE bool DL_SYSCTL_isBeeperEnabled | ( | void | ) |

Check if Beeper is enabled.

| true | The Beeper output is enabled |

| false | The Beeper output is disabled |

| __STATIC_INLINE bool DL_SYSCTL_isFlashBankSwapEnabled | ( | void | ) |

Checks if Flash Bank swapping is enabled.

| false | This is not a multi-bank device |

| __STATIC_INLINE bool DL_SYSCTL_isExecuteFromUpperFlashBank | ( | void | ) |

Checks if executing from upper flash bank.

| false | This is not a multi-bank device. |