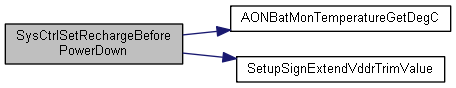

Set Recharge values before entering Power Down.

This function shall be called just before entering Power Down. It calculates an optimal and safe recharge setting of the adaptive recharge controller. The results of previous setting are also taken into account.

96 int32_t deltaVddrSleepTrim ;

97 int32_t vddrTrimSleep ;

98 int32_t vddrTrimActve ;

99 int32_t diffVddrActiveSleep ;

100 uint32_t ccfg_ModeConfReg ;

102 uint32_t prcmRamRetention ;

111 uint32_t newRechargePeriod ;

114 const uint32_t * pLookupTable ;

133 deltaVddrSleepTrim = ((((int32_t) ccfg_ModeConfReg )

138 int32_t tcDelta = ( 62 - curTemp ) >> 3;

139 if ( tcDelta > 8 ) tcDelta = 8;

140 if ( tcDelta > deltaVddrSleepTrim ) deltaVddrSleepTrim = tcDelta;

164 vddrTrimSleep += deltaVddrSleepTrim;

165 if ( vddrTrimSleep > 21 ) vddrTrimSleep = 21;

166 if ( vddrTrimSleep < -10 ) vddrTrimSleep = -10;

185 shiftedTemp = curTemp - 15;

198 if ( shiftedTemp >= 0 ) {

200 shiftedTemp += ( shiftedTemp << 4 );

203 ti = ( shiftedTemp >> 8 );

213 cd = pLookupTable[ dii + 1 ] - pLookupTable[ dii ];

220 di += (( cd >> 8 ) & 0xFF );

223 di += (( cd >> 16 ) & 0xFF );

226 di += (( cd >> 24 ) & 0xFF );

234 cl = pLookupTable[ ti ];

240 if ( curState & PD_STATE_XOSC_LPM ) {

241 load += (( cl >> 8 ) & 0xFF );

243 if ( curState & PD_STATE_RFMEM_RET ) {

244 load += (( cl >> 16 ) & 0xFF );

247 load += (( cl >> 24 ) & 0xFF );

251 load += ((( di * ( shiftedTemp - ( ti << 8 ))) + 128 ) >> 8 );

258 diffVddrActiveSleep = ( vddrTrimActve - vddrTrimSleep );

259 if ( diffVddrActiveSleep < 1 ) diffVddrActiveSleep = 1;

260 k = ( diffVddrActiveSleep * 52 );

266 newRechargePeriod = ( vddrCap * k ) / load;

267 if ( newRechargePeriod > 0xFFFF ) {

268 newRechargePeriod = 0xFFFF;

273 if ( curTemp > 127 ) curTemp = 127;

274 if ( curTemp < -128 ) curTemp = -128;

290 while ( perM > 511 ) {

294 perM = ( perM - 15 ) >> 4;

#define XOSC_IN_HIGH_POWER_MODE

Definition: sys_ctrl.h:134

static int32_t SetupSignExtendVddrTrimValue(uint32_t ui32VddrTrimVal)

Sign extend the VDDR_TRIM setting (special format ranging from -10 to +21)

Definition: setup_rom.h:317

int8_t pdTemp

Definition: sys_ctrl.c:80

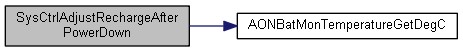

int32_t AONBatMonTemperatureGetDegC(void)

Get the current temperature measurement as a signed value in Deg Celsius.

Definition: aon_batmon.c:60

uint8_t pdState

Definition: sys_ctrl.c:79

#define PD_STATE_XOSC_LPM

Definition: sys_ctrl.c:73

#define PD_STATE_CACHE_RET

Definition: sys_ctrl.c:71

#define PD_STATE_EXT_REG_MODE

Definition: sys_ctrl.c:74

static PowerQualGlobals_t powerQualGlobals

Definition: sys_ctrl.c:83

#define PD_STATE_RFMEM_RET

Definition: sys_ctrl.c:72

uint32_t pdTime

Definition: sys_ctrl.c:77

uint16_t pdRechargePeriod

Definition: sys_ctrl.c:78