|

|

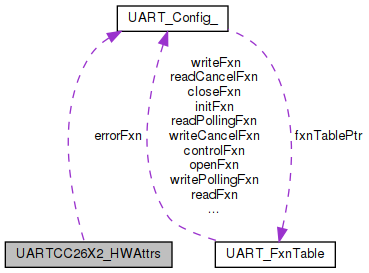

UARTCC26X2 Hardware attributes. More...

#include <UARTCC26X2.h>

Data Fields | |

| uint32_t | baseAddr |

| int | intNum |

| uint8_t | intPriority |

| uint32_t | swiPriority |

| Swi priority. The higher the number, the higher the priority. The minimum priority is 0 and the maximum is defined by the underlying OS. More... | |

| uint32_t | flowControl |

| unsigned char * | ringBufPtr |

| size_t | ringBufSize |

| uint8_t | rxPin |

| uint8_t | txPin |

| uint8_t | ctsPin |

| uint8_t | rtsPin |

| UARTCC26X2_FifoThreshold | txIntFifoThr |

| UARTCC26X2_FifoThreshold | rxIntFifoThr |

| UARTCC26X2_ErrorCallback | errorFxn |

UARTCC26X2 Hardware attributes.

The fields, baseAddr and intNum are used by driverlib APIs and therefore must be populated by driverlib macro definitions. These definitions are found under the device family in:

intPriority is the UART peripheral's interrupt priority, as defined by the underlying OS. It is passed unmodified to the underlying OS's interrupt handler creation code, so you need to refer to the OS documentation for usage. For example, for SYS/BIOS applications, refer to the ti.sysbios.family.arm.m3.Hwi documentation for SYS/BIOS usage of interrupt priorities. If the driver uses the ti.dpl interface instead of making OS calls directly, then the HwiP port handles the interrupt priority in an OS specific way. In the case of the SYS/BIOS port, intPriority is passed unmodified to Hwi_create(). The CC26xx uses three of the priority bits, meaning ~0 has the same effect as (7 << 5).

(7 << 5) will apply the lowest priority. (1 << 5) will apply the highest priority.

Setting the priority to 0 is not supported by this driver. HWI's with priority 0 ignore the HWI dispatcher to support zero-latency interrupts, thus invalidating the critical sections in this driver.

A sample structure is shown below:

The .ctsPin and .rtsPin must be assigned to enable flow control.

| uint32_t UARTCC26X2_HWAttrs::baseAddr |

UART Peripheral's base address

| int UARTCC26X2_HWAttrs::intNum |

UART Peripheral's interrupt vector

| uint8_t UARTCC26X2_HWAttrs::intPriority |

UART Peripheral's interrupt priority

| uint32_t UARTCC26X2_HWAttrs::swiPriority |

Swi priority. The higher the number, the higher the priority. The minimum priority is 0 and the maximum is defined by the underlying OS.

| uint32_t UARTCC26X2_HWAttrs::flowControl |

Hardware flow control setting

| unsigned char* UARTCC26X2_HWAttrs::ringBufPtr |

Pointer to an application ring buffer

| size_t UARTCC26X2_HWAttrs::ringBufSize |

Size of ringBufPtr

| uint8_t UARTCC26X2_HWAttrs::rxPin |

UART RX pin assignment

| uint8_t UARTCC26X2_HWAttrs::txPin |

UART TX pin assignment

| uint8_t UARTCC26X2_HWAttrs::ctsPin |

UART clear to send (CTS) pin assignment

| uint8_t UARTCC26X2_HWAttrs::rtsPin |

UART request to send (RTS) pin assignment

| UARTCC26X2_FifoThreshold UARTCC26X2_HWAttrs::txIntFifoThr |

UART TX interrupt FIFO threshold select

| UARTCC26X2_FifoThreshold UARTCC26X2_HWAttrs::rxIntFifoThr |

UART RX interrupt FIFO threshold select

| UARTCC26X2_ErrorCallback UARTCC26X2_HWAttrs::errorFxn |

Application error function to be called on receive errors