|

|

|

MSPM0C110X Driver Library

2.02.00.05

|

|

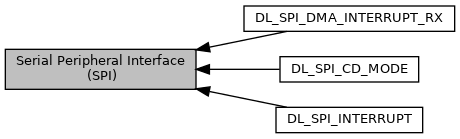

Modules | |

| DL_SPI_CD_MODE | |

| DL_SPI_INTERRUPT | |

| DL_SPI_DMA_INTERRUPT_RX | |

Data Structures | |

| struct | DL_SPI_Config |

| Configuration struct for DL_SPI_init. More... | |

| struct | DL_SPI_ClockConfig |

| Configuration struct for DL_SPI_setClockConfig. More... | |

| struct | DL_SPI_backupConfig |

| Configuration structure to backup SPI peripheral state before going to STOP/STANDBY mode. Not required after PG 1.0 silicon. Used by DL_SPI_saveConfiguration and DL_SPI_restoreConfiguration. More... | |

Macros | |

| #define | DL_SPI_DMA_INTERRUPT_TX (SPI_DMA_TRIG_TX_IMASK_TX_SET) |

| SPI interrupt for enabling SPI transmit as DMA trigger. | |

Enumerations | |

| enum | DL_SPI_DMA_IIDX_RX { DL_SPI_DMA_IIDX_RX_TRIGGER = SPI_DMA_TRIG_RX_IIDX_STAT_RX_EVT, DL_SPI_DMA_IIDX_RX_TIMEOUT_TRIGGER = SPI_DMA_TRIG_RX_IIDX_STAT_RTOUT_EVT } |

| enum | DL_SPI_DMA_IIDX_TX { DL_SPI_DMA_IIDX_TX_TRIGGER = SPI_DMA_TRIG_TX_IIDX_STAT_TX_EVT } |

| enum | DL_SPI_PARITY { DL_SPI_PARITY_EVEN, DL_SPI_PARITY_ODD, DL_SPI_PARITY_NONE = (SPI_CTL1_PREN_DISABLE | SPI_CTL1_PTEN_DISABLE) } |

| enum | DL_SPI_FRAME_FORMAT { DL_SPI_FRAME_FORMAT_MOTO3_POL0_PHA0, DL_SPI_FRAME_FORMAT_MOTO3_POL0_PHA1, DL_SPI_FRAME_FORMAT_MOTO3_POL1_PHA0, DL_SPI_FRAME_FORMAT_MOTO3_POL1_PHA1, DL_SPI_FRAME_FORMAT_MOTO4_POL0_PHA0, DL_SPI_FRAME_FORMAT_MOTO4_POL0_PHA1, DL_SPI_FRAME_FORMAT_MOTO4_POL1_PHA0, DL_SPI_FRAME_FORMAT_MOTO4_POL1_PHA1, DL_SPI_FRAME_FORMAT_TI_SYNC = (SPI_CTL0_FRF_TI_SYNC) } |

| enum | DL_SPI_MODE { DL_SPI_MODE_CONTROLLER = (SPI_CTL1_CP_ENABLE), DL_SPI_MODE_PERIPHERAL = (SPI_CTL1_CP_DISABLE) } |

| enum | DL_SPI_BIT_ORDER { DL_SPI_BIT_ORDER_MSB_FIRST = (SPI_CTL1_MSB_ENABLE), DL_SPI_BIT_ORDER_LSB_FIRST = (SPI_CTL1_MSB_DISABLE) } |

| enum | DL_SPI_DATA_SIZE { DL_SPI_DATA_SIZE_4 = (SPI_CTL0_DSS_DSS_4), DL_SPI_DATA_SIZE_5 = (SPI_CTL0_DSS_DSS_5), DL_SPI_DATA_SIZE_6 = (SPI_CTL0_DSS_DSS_6), DL_SPI_DATA_SIZE_7 = (SPI_CTL0_DSS_DSS_7), DL_SPI_DATA_SIZE_8 = (SPI_CTL0_DSS_DSS_8), DL_SPI_DATA_SIZE_9 = (SPI_CTL0_DSS_DSS_9), DL_SPI_DATA_SIZE_10 = (SPI_CTL0_DSS_DSS_10), DL_SPI_DATA_SIZE_11 = (SPI_CTL0_DSS_DSS_11), DL_SPI_DATA_SIZE_12 = (SPI_CTL0_DSS_DSS_12), DL_SPI_DATA_SIZE_13 = (SPI_CTL0_DSS_DSS_13), DL_SPI_DATA_SIZE_14 = (SPI_CTL0_DSS_DSS_14), DL_SPI_DATA_SIZE_15 = (SPI_CTL0_DSS_DSS_15), DL_SPI_DATA_SIZE_16 = (SPI_CTL0_DSS_DSS_16) } |

| enum | DL_SPI_CHIP_SELECT { DL_SPI_CHIP_SELECT_0 = (SPI_CTL0_CSSEL_CSSEL_0), DL_SPI_CHIP_SELECT_1 = (SPI_CTL0_CSSEL_CSSEL_1), DL_SPI_CHIP_SELECT_2 = (SPI_CTL0_CSSEL_CSSEL_2), DL_SPI_CHIP_SELECT_3 = (SPI_CTL0_CSSEL_CSSEL_3), DL_SPI_CHIP_SELECT_NONE = (0) } |

| enum | DL_SPI_TX_FIFO_LEVEL { DL_SPI_TX_FIFO_LEVEL_3_4_EMPTY = SPI_IFLS_TXIFLSEL_LVL_3_4, DL_SPI_TX_FIFO_LEVEL_1_2_EMPTY = SPI_IFLS_TXIFLSEL_LVL_1_2, DL_SPI_TX_FIFO_LEVEL_1_4_EMPTY = SPI_IFLS_TXIFLSEL_LVL_1_4, DL_SPI_TX_FIFO_LEVEL_EMPTY = SPI_IFLS_TXIFLSEL_LVL_EMPTY, DL_SPI_TX_FIFO_LEVEL_ONE_FRAME = SPI_IFLS_TXIFLSEL_LEVEL_1 } |

| enum | DL_SPI_RX_FIFO_LEVEL { DL_SPI_RX_FIFO_LEVEL_ONE_FRAME = SPI_IFLS_RXIFLSEL_LEVEL_1, DL_SPI_RX_FIFO_LEVEL_FULL = SPI_IFLS_RXIFLSEL_LVL_FULL, DL_SPI_RX_FIFO_LEVEL_3_4_FULL = SPI_IFLS_RXIFLSEL_LVL_3_4, DL_SPI_RX_FIFO_LEVEL_1_2_FULL = SPI_IFLS_RXIFLSEL_LVL_1_2, DL_SPI_RX_FIFO_LEVEL_1_4_FULL = SPI_IFLS_RXIFLSEL_LVL_1_4 } |

| enum | DL_SPI_IIDX { DL_SPI_IIDX_DMA_DONE_TX = SPI_CPU_INT_IIDX_STAT_DMA_DONE_TX_EVT, DL_SPI_IIDX_DMA_DONE_RX = SPI_CPU_INT_IIDX_STAT_DMA_DONE_RX_EVT, DL_SPI_IIDX_IDLE = SPI_CPU_INT_IIDX_STAT_IDLE_EVT, DL_SPI_IIDX_TX_EMPTY = SPI_CPU_INT_IIDX_STAT_TX_EMPTY, DL_SPI_IIDX_TX = SPI_CPU_INT_IIDX_STAT_TX_EVT, DL_SPI_IIDX_RX = SPI_CPU_INT_IIDX_STAT_RX_EVT, DL_SPI_IIDX_RX_TIMEOUT = SPI_CPU_INT_IIDX_STAT_RTOUT_EVT, DL_SPI_IIDX_RX_FULL = SPI_CPU_INT_IIDX_STAT_RXFULL_EVT, DL_SPI_IIDX_TX_UNDERFLOW = SPI_CPU_INT_IIDX_STAT_TXFIFO_UNF_EVT, DL_SPI_IIDX_PARITY_ERROR = SPI_CPU_INT_IIDX_STAT_PER_EVT, DL_SPI_IIDX_RX_OVERFLOW = SPI_CPU_INT_IIDX_STAT_RXFIFO_OFV_EVT } |

| enum | DL_SPI_CLOCK_DIVIDE_RATIO { DL_SPI_CLOCK_DIVIDE_RATIO_1 = SPI_CLKDIV_RATIO_DIV_BY_1, DL_SPI_CLOCK_DIVIDE_RATIO_2 = SPI_CLKDIV_RATIO_DIV_BY_2, DL_SPI_CLOCK_DIVIDE_RATIO_3 = SPI_CLKDIV_RATIO_DIV_BY_3, DL_SPI_CLOCK_DIVIDE_RATIO_4 = SPI_CLKDIV_RATIO_DIV_BY_4, DL_SPI_CLOCK_DIVIDE_RATIO_5 = SPI_CLKDIV_RATIO_DIV_BY_5, DL_SPI_CLOCK_DIVIDE_RATIO_6 = SPI_CLKDIV_RATIO_DIV_BY_6, DL_SPI_CLOCK_DIVIDE_RATIO_7 = SPI_CLKDIV_RATIO_DIV_BY_7, DL_SPI_CLOCK_DIVIDE_RATIO_8 = SPI_CLKDIV_RATIO_DIV_BY_8 } |

| enum | DL_SPI_CLOCK { DL_SPI_CLOCK_BUSCLK = SPI_CLKSEL_SYSCLK_SEL_ENABLE, DL_SPI_CLOCK_MFCLK = SPI_CLKSEL_MFCLK_SEL_ENABLE, DL_SPI_CLOCK_LFCLK = SPI_CLKSEL_LFCLK_SEL_ENABLE } |

Functions | |

| void | DL_SPI_init (SPI_Regs *spi, DL_SPI_Config *config) |

| Initialize the SPI peripheral. More... | |

| __STATIC_INLINE void | DL_SPI_enablePower (SPI_Regs *spi) |

| Enables power on SPI module. More... | |

| __STATIC_INLINE void | DL_SPI_disablePower (SPI_Regs *spi) |

| Disables power on spi module. More... | |

| __STATIC_INLINE bool | DL_SPI_isPowerEnabled (SPI_Regs *spi) |

| Returns if power on spi module. More... | |

| __STATIC_INLINE void | DL_SPI_reset (SPI_Regs *spi) |

| Resets spi peripheral. More... | |

| __STATIC_INLINE bool | DL_SPI_isReset (SPI_Regs *spi) |

| Returns if spi peripheral was reset. More... | |

| __STATIC_INLINE void | DL_SPI_enable (SPI_Regs *spi) |

| Enable the SPI peripheral. More... | |

| __STATIC_INLINE bool | DL_SPI_isEnabled (SPI_Regs *spi) |

| Checks if the SPI peripheral is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_disable (SPI_Regs *spi) |

| Disable the SPI peripheral. More... | |

| void | DL_SPI_setClockConfig (SPI_Regs *spi, DL_SPI_ClockConfig *config) |

| Configure SPI source clock. More... | |

| void | DL_SPI_getClockConfig (SPI_Regs *spi, DL_SPI_ClockConfig *config) |

| Get SPI source clock configuration. More... | |

| __STATIC_INLINE bool | DL_SPI_isBusy (SPI_Regs *spi) |

| Checks if the SPI is busy transmitting. More... | |

| __STATIC_INLINE bool | DL_SPI_isTXFIFOEmpty (SPI_Regs *spi) |

| Checks if the TX FIFO is empty. More... | |

| __STATIC_INLINE bool | DL_SPI_isTXFIFOFull (SPI_Regs *spi) |

| Checks if the TX FIFO is full. More... | |

| __STATIC_INLINE bool | DL_SPI_isRXFIFOEmpty (SPI_Regs *spi) |

| Checks if the RX FIFO is empty. More... | |

| __STATIC_INLINE bool | DL_SPI_isRXFIFOFull (SPI_Regs *spi) |

| Checks if the RX FIFO is full. More... | |

| __STATIC_INLINE void | DL_SPI_setParity (SPI_Regs *spi, DL_SPI_PARITY parity) |

| Sets the parity configuration used for transactions. More... | |

| __STATIC_INLINE DL_SPI_PARITY | DL_SPI_getParity (SPI_Regs *spi) |

| Get the current receive and transmit parity configuration. More... | |

| __STATIC_INLINE void | DL_SPI_enableReceiveParity (SPI_Regs *spi) |

| Enables receive parity. More... | |

| __STATIC_INLINE void | DL_SPI_disableReceiveParity (SPI_Regs *spi) |

| Disables receive parity. More... | |

| __STATIC_INLINE bool | DL_SPI_isReceiveParityEnabled (SPI_Regs *spi) |

| Checks if receive parity is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_enableTransmitParity (SPI_Regs *spi) |

| Enables transmit parity. More... | |

| __STATIC_INLINE void | DL_SPI_disableTransmitParity (SPI_Regs *spi) |

| Disables transmit parity. More... | |

| __STATIC_INLINE bool | DL_SPI_isTransmitParityEnabled (SPI_Regs *spi) |

| Checks if transmit parity is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_setFrameFormat (SPI_Regs *spi, DL_SPI_FRAME_FORMAT frameFormat) |

| Set the frame format to use. More... | |

| __STATIC_INLINE DL_SPI_FRAME_FORMAT | DL_SPI_getFrameFormat (SPI_Regs *spi) |

| Get the frame format configuration. More... | |

| __STATIC_INLINE void | DL_SPI_setDataSize (SPI_Regs *spi, DL_SPI_DATA_SIZE dataSize) |

| Set the size for transfers. More... | |

| __STATIC_INLINE DL_SPI_DATA_SIZE | DL_SPI_getDataSize (SPI_Regs *spi) |

| Get the configured size for transfers. More... | |

| __STATIC_INLINE void | DL_SPI_setMode (SPI_Regs *spi, DL_SPI_MODE mode) |

| Set whether the device should be in controller/peripheral mode. More... | |

| __STATIC_INLINE DL_SPI_MODE | DL_SPI_getMode (SPI_Regs *spi) |

| Get the current mode for the SPI (controller/peripheral) More... | |

| __STATIC_INLINE void | DL_SPI_setBitOrder (SPI_Regs *spi, DL_SPI_BIT_ORDER bitOrder) |

| Set the bit order used for transfers. More... | |

| __STATIC_INLINE DL_SPI_BIT_ORDER | DL_SPI_getBitOrder (SPI_Regs *spi) |

| Get the current bit order used for transfers. More... | |

| __STATIC_INLINE void | DL_SPI_enableLoopbackMode (SPI_Regs *spi) |

| Enables loopback mode. More... | |

| __STATIC_INLINE void | DL_SPI_disableLoopbackMode (SPI_Regs *spi) |

| Disables loopback mode. More... | |

| __STATIC_INLINE bool | DL_SPI_isLoopbackModeEnabled (SPI_Regs *spi) |

| Checks if the loopback mode is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_setRepeatTransmit (SPI_Regs *spi, uint32_t numRepeats) |

| Set counter for repeated transmit. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getRepeatTransmit (SPI_Regs *spi) |

| Get counter for repeated transmit. More... | |

| __STATIC_INLINE void | DL_SPI_enablePeripheralAlignDataOnChipSelect (SPI_Regs *spi) |

| Enables data alignment on chip select for peripherals. More... | |

| __STATIC_INLINE void | DL_SPI_disablePeripheralAlignDataOnChipSelect (SPI_Regs *spi) |

| Disables data alignment on chip select for peripherals. More... | |

| __STATIC_INLINE bool | DL_SPI_isPeripheralAlignDataOnChipSelectEnabled (SPI_Regs *spi) |

| Checks if data alignment on chip select for peripherals is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_enablePacking (SPI_Regs *spi) |

| Enables packing feature. More... | |

| __STATIC_INLINE void | DL_SPI_disablePacking (SPI_Regs *spi) |

| Disables packing feature. More... | |

| __STATIC_INLINE bool | DL_SPI_isPackingEnabled (SPI_Regs *spi) |

| Checks if packing feature is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_setChipSelect (SPI_Regs *spi, DL_SPI_CHIP_SELECT chipSelect) |

| Set chip select used for controller or peripheral mode. More... | |

| __STATIC_INLINE DL_SPI_CHIP_SELECT | DL_SPI_getChipSelect (SPI_Regs *spi) |

| Get chip select used for controller or peripheral mode. More... | |

| __STATIC_INLINE void | DL_SPI_setPeripheralReceiveTimeout (SPI_Regs *spi, uint32_t timeout) |

| Set peripheral receive timeout. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getPeripheralReceiveTimeout (SPI_Regs *spi) |

| Get peripheral receive timeout. More... | |

| __STATIC_INLINE void | DL_SPI_setControllerCommandDataModeConfig (SPI_Regs *spi, uint32_t config) |

| Configure the command/data mode. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getControllerCommandDataModeConfig (SPI_Regs *spi) |

| Get the command/data mode configuration. More... | |

| __STATIC_INLINE void | DL_SPI_enableControllerCommandDataMode (SPI_Regs *spi) |

| Enables command/data mode. More... | |

| __STATIC_INLINE void | DL_SPI_disableControllerCommandDataMode (SPI_Regs *spi) |

| Disables command/data mode. More... | |

| __STATIC_INLINE bool | DL_SPI_isControllerCommandDataModeEnabled (SPI_Regs *spi) |

| Checks if command/data mode is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_enablePeripheralDataOutput (SPI_Regs *spi) |

| Enables peripheral data output. More... | |

| __STATIC_INLINE void | DL_SPI_disablePeripheralDataOutput (SPI_Regs *spi) |

| Disables peripheral data output. More... | |

| __STATIC_INLINE bool | DL_SPI_isPeripheralDataOutputEnabled (SPI_Regs *spi) |

| Checks if peripheral data output is enabled. More... | |

| __STATIC_INLINE void | DL_SPI_setDelayedSampling (SPI_Regs *spi, uint32_t delay) |

| Set the delay sampling. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getDelayedSampling (SPI_Regs *spi) |

| Get the delay sampling. More... | |

| __STATIC_INLINE void | DL_SPI_setFIFOThreshold (SPI_Regs *spi, DL_SPI_RX_FIFO_LEVEL rxThreshold, DL_SPI_TX_FIFO_LEVEL txThreshold) |

| Set the RX and TX FIFO interrupt threshold level. More... | |

| __STATIC_INLINE DL_SPI_TX_FIFO_LEVEL | DL_SPI_getTXFIFOThreshold (SPI_Regs *spi) |

| Get the TX FIFO interrupt threshold level. More... | |

| __STATIC_INLINE DL_SPI_RX_FIFO_LEVEL | DL_SPI_getRXFIFOThreshold (SPI_Regs *spi) |

| Get the RX FIFO interrupt threshold level. More... | |

| __STATIC_INLINE void | DL_SPI_setBitRateSerialClockDivider (SPI_Regs *spi, uint32_t SCR) |

| Set the SPI bit rate serial clock divider (SCR) More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getBitRateSerialClockDivider (SPI_Regs *spi) |

| Get the SPI bit rate serial clock divider (SCR) More... | |

| __STATIC_INLINE void | DL_SPI_transmitData8 (SPI_Regs *spi, uint8_t data) |

| Writes 8-bit data into the TX FIFO for transmit. More... | |

| __STATIC_INLINE void | DL_SPI_transmitData16 (SPI_Regs *spi, uint16_t data) |

| Writes 16-bit data into the TX FIFO for transmit. More... | |

| __STATIC_INLINE void | DL_SPI_transmitData32 (SPI_Regs *spi, uint32_t data) |

| Writes 32-bit data into the TX FIFO for transmit. More... | |

| __STATIC_INLINE uint8_t | DL_SPI_receiveData8 (SPI_Regs *spi) |

| Reads 8-bit data from the RX FIFO. More... | |

| __STATIC_INLINE uint16_t | DL_SPI_receiveData16 (SPI_Regs *spi) |

| Reads 16-bit data from the RX FIFO. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_receiveData32 (SPI_Regs *spi) |

| Reads 32-bit data from the RX FIFO. More... | |

| __STATIC_INLINE void | DL_SPI_enableInterrupt (SPI_Regs *spi, uint32_t interruptMask) |

| Enable SPI interrupts. More... | |

| __STATIC_INLINE void | DL_SPI_disableInterrupt (SPI_Regs *spi, uint32_t interruptMask) |

| Disable SPI interrupts. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledInterrupts (SPI_Regs *spi, uint32_t interruptMask) |

| Check which SPI interrupts are enabled. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledInterruptStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Check interrupt flag of enabled SPI interrupts. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getRawInterruptStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Check interrupt flag of any SPI interrupt. More... | |

| __STATIC_INLINE DL_SPI_IIDX | DL_SPI_getPendingInterrupt (SPI_Regs *spi) |

| Get highest priority pending SPI interrupt. More... | |

| __STATIC_INLINE void | DL_SPI_clearInterruptStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Clear pending SPI interrupts. More... | |

| void | DL_SPI_transmitDataBlocking8 (SPI_Regs *spi, uint8_t data) |

| Blocks to ensure transmit is ready before sending data. More... | |

| void | DL_SPI_transmitDataBlocking16 (SPI_Regs *spi, uint16_t data) |

| Blocks to ensure transmit is ready before sending data. More... | |

| void | DL_SPI_transmitDataBlocking32 (SPI_Regs *spi, uint32_t data) |

| Blocks to ensure transmit is ready before sending data. More... | |

| uint8_t | DL_SPI_receiveDataBlocking8 (SPI_Regs *spi) |

| Blocks to ensure receive is ready before reading data. More... | |

| uint16_t | DL_SPI_receiveDataBlocking16 (SPI_Regs *spi) |

| Blocks to ensure receive is ready before reading data. More... | |

| uint32_t | DL_SPI_receiveDataBlocking32 (SPI_Regs *spi) |

| Blocks to ensure receive is ready before reading data. More... | |

| bool | DL_SPI_transmitDataCheck8 (SPI_Regs *spi, uint8_t data) |

| Checks the TX FIFO before trying to transmit data. More... | |

| bool | DL_SPI_transmitDataCheck16 (SPI_Regs *spi, uint16_t data) |

| Checks the TX FIFO before trying to transmit data. More... | |

| bool | DL_SPI_transmitDataCheck32 (SPI_Regs *spi, uint32_t data) |

| Checks the TX FIFO before trying to transmit data. More... | |

| bool | DL_SPI_receiveDataCheck8 (SPI_Regs *spi, uint8_t *buffer) |

| Checks the RX FIFO before trying to transmit data. More... | |

| bool | DL_SPI_receiveDataCheck16 (SPI_Regs *spi, uint16_t *buffer) |

| Checks the RX FIFO before trying to transmit data. More... | |

| bool | DL_SPI_receiveDataCheck32 (SPI_Regs *spi, uint32_t *buffer) |

| Checks the RX FIFO before trying to transmit data. More... | |

| uint32_t | DL_SPI_drainRXFIFO8 (SPI_Regs *spi, uint8_t *buffer, uint32_t maxCount) |

| Read all available data out of the RX FIFO using 8 bit access. More... | |

| uint32_t | DL_SPI_drainRXFIFO16 (SPI_Regs *spi, uint16_t *buffer, uint32_t maxCount) |

| Read all available data out of the RX FIFO using 16 bit access. More... | |

| uint32_t | DL_SPI_drainRXFIFO32 (SPI_Regs *spi, uint32_t *buffer, uint32_t maxCount) |

| Read all available data out of the RX FIFO using 32 bit access. More... | |

| uint32_t | DL_SPI_fillTXFIFO8 (SPI_Regs *spi, uint8_t *buffer, uint32_t count) |

| Fill the TX FIFO using 8 bit access. More... | |

| uint32_t | DL_SPI_fillTXFIFO16 (SPI_Regs *spi, uint16_t *buffer, uint32_t count) |

| Fill the TX FIFO using 16 bit access. More... | |

| uint32_t | DL_SPI_fillTXFIFO32 (SPI_Regs *spi, uint32_t *buffer, uint32_t count) |

| Fill the TX FIFO using 32 bit access. More... | |

| __STATIC_INLINE void | DL_SPI_enableDMAReceiveEvent (SPI_Regs *spi, uint32_t interrupt) |

| Enable SPI interrupt for triggering the DMA receive event. More... | |

| __STATIC_INLINE void | DL_SPI_enableDMATransmitEvent (SPI_Regs *spi) |

| Enable SPI interrupt for triggering the DMA transmit event. More... | |

| __STATIC_INLINE void | DL_SPI_disableDMAReceiveEvent (SPI_Regs *spi, uint32_t interrupt) |

| Disables SPI interrupt from triggering the DMA receive event. More... | |

| __STATIC_INLINE void | DL_SPI_disableDMATransmitEvent (SPI_Regs *spi) |

| Disables SPI interrupt from triggering the DMA transmit event. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledDMAReceiveEvent (SPI_Regs *spi, uint32_t interruptMask) |

| Check which SPI interrupt for DMA receive events is enabled. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledDMATransmitEvent (SPI_Regs *spi) |

| Check if SPI interrupt for DMA transmit event is enabled. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledDMAReceiveEventStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Check interrupt flag of enabled SPI interrupt for DMA receive event. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getEnabledDMATransmitEventStatus (SPI_Regs *spi) |

| Check interrupt flag of enabled SPI interrupt for DMA transmit event. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getRawDMAReceiveEventStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Check interrupt flag of any SPI interrupt for DMA receive event. More... | |

| __STATIC_INLINE uint32_t | DL_SPI_getRawDMATransmitEventStatus (SPI_Regs *spi) |

| Check interrupt flag of any SPI interrupt for DMA transmit event. More... | |

| __STATIC_INLINE DL_SPI_DMA_IIDX_RX | DL_SPI_getPendingDMAReceiveEvent (SPI_Regs *spi) |

| Get highest priority pending SPI interrupt for DMA receive event. More... | |

| __STATIC_INLINE DL_SPI_DMA_IIDX_TX | DL_SPI_getPendingDMATransmitEvent (SPI_Regs *spi) |

| Get highest priority pending SPI interrupt for DMA transmit event. More... | |

| __STATIC_INLINE void | DL_SPI_clearDMAReceiveEventStatus (SPI_Regs *spi, uint32_t interruptMask) |

| Clear pending SPI interrupts for DMA receive event. More... | |

| __STATIC_INLINE void | DL_SPI_clearDMATransmitEventStatus (SPI_Regs *spi) |

| Clear pending SPI interrupt for DMA transmit event. More... | |

| bool | DL_SPI_saveConfiguration (SPI_Regs *spi, DL_SPI_backupConfig *ptr) |

| Save SPI configuration before entering a power loss state. More... | |

| bool | DL_SPI_restoreConfiguration (SPI_Regs *spi, DL_SPI_backupConfig *ptr) |

| Restore SPI configuration after leaving a power loss state. More... | |

The Serial Peripheral Interface Driver Library allows full configuration of the MSPM0 SPI module. The serial peripheral interface (SPI) module provides a standardized serial interface to transfer data between MSPM0 devices and other external devices with SPI interface.

| enum DL_SPI_DMA_IIDX_RX |

| enum DL_SPI_DMA_IIDX_TX |

| enum DL_SPI_PARITY |

| enum DL_SPI_FRAME_FORMAT |

| enum DL_SPI_MODE |

| enum DL_SPI_BIT_ORDER |

| enum DL_SPI_DATA_SIZE |

| enum DL_SPI_CHIP_SELECT |

| enum DL_SPI_TX_FIFO_LEVEL |

| enum DL_SPI_RX_FIFO_LEVEL |

| enum DL_SPI_IIDX |

| enum DL_SPI_CLOCK |

| void DL_SPI_init | ( | SPI_Regs * | spi, |

| DL_SPI_Config * | config | ||

| ) |

Initialize the SPI peripheral.

Initializes all the common configurable options for the SPI peripheral. Any other custom configuration can be done after calling this API. The SPI is not enabled in this API.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | config | Configuration for SPI peripheral |

| __STATIC_INLINE void DL_SPI_enablePower | ( | SPI_Regs * | spi | ) |

Enables power on SPI module.

| spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disablePower | ( | SPI_Regs * | spi | ) |

Disables power on spi module.

| spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isPowerEnabled | ( | SPI_Regs * | spi | ) |

Returns if power on spi module.

| spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_reset | ( | SPI_Regs * | spi | ) |

Resets spi peripheral.

| spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isReset | ( | SPI_Regs * | spi | ) |

Returns if spi peripheral was reset.

| spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_enable | ( | SPI_Regs * | spi | ) |

Enable the SPI peripheral.

| [in] | spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isEnabled | ( | SPI_Regs * | spi | ) |

Checks if the SPI peripheral is enabled.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The SPI peripheral is enabled |

| false | The SPI peripheral is disabled |

| __STATIC_INLINE void DL_SPI_disable | ( | SPI_Regs * | spi | ) |

Disable the SPI peripheral.

| [in] | spi | Pointer to the register overlay for the peripheral |

References DL_SPI_getClockConfig(), and DL_SPI_setClockConfig().

| void DL_SPI_setClockConfig | ( | SPI_Regs * | spi, |

| DL_SPI_ClockConfig * | config | ||

| ) |

Configure SPI source clock.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | config | Pointer to the clock configuration struct DL_SPI_ClockConfig. |

Referenced by DL_SPI_disable().

| void DL_SPI_getClockConfig | ( | SPI_Regs * | spi, |

| DL_SPI_ClockConfig * | config | ||

| ) |

Get SPI source clock configuration.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | config | Pointer to the clock configuration struct DL_SPI_ClockConfig. |

Referenced by DL_SPI_disable().

| __STATIC_INLINE bool DL_SPI_isBusy | ( | SPI_Regs * | spi | ) |

Checks if the SPI is busy transmitting.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The SPI is transmitting |

| false | The SPI is idle |

| __STATIC_INLINE bool DL_SPI_isTXFIFOEmpty | ( | SPI_Regs * | spi | ) |

Checks if the TX FIFO is empty.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The TX FIFO is empty |

| false | The TX FIFO is not empty |

| __STATIC_INLINE bool DL_SPI_isTXFIFOFull | ( | SPI_Regs * | spi | ) |

Checks if the TX FIFO is full.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The TX FIFO is full |

| false | The TX FIFO is not full |

| __STATIC_INLINE bool DL_SPI_isRXFIFOEmpty | ( | SPI_Regs * | spi | ) |

Checks if the RX FIFO is empty.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The RX FIFO is empty |

| false | The RX FIFO is not empty |

| __STATIC_INLINE bool DL_SPI_isRXFIFOFull | ( | SPI_Regs * | spi | ) |

Checks if the RX FIFO is full.

| [in] | spi | Pointer to the register overlay for the peripheral |

| true | The RX FIFO is full |

| false | The RX FIFO is not full |

| __STATIC_INLINE void DL_SPI_setParity | ( | SPI_Regs * | spi, |

| DL_SPI_PARITY | parity | ||

| ) |

Sets the parity configuration used for transactions.

This API sets the configuration for both receive parity and transmit parity. This includes which bit is used, and whether even or odd parity is set.

To individually enable or dsiable the receive or transmit parity, refer to the APIs listed below.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | parity | Parity configuration to use. One of DL_SPI_PARITY. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_PARITY DL_SPI_getParity | ( | SPI_Regs * | spi | ) |

Get the current receive and transmit parity configuration.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_PARITY |

| __STATIC_INLINE void DL_SPI_enableReceiveParity | ( | SPI_Regs * | spi | ) |

Enables receive parity.

This API only enables receive parity, it does not configure the parity mode used.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disableReceiveParity | ( | SPI_Regs * | spi | ) |

Disables receive parity.

This API only disable receive parity, it does not configure the parity mode used.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isReceiveParityEnabled | ( | SPI_Regs * | spi | ) |

Checks if receive parity is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | Receive parity is enabled |

| false | Receive parity is disabled |

| __STATIC_INLINE void DL_SPI_enableTransmitParity | ( | SPI_Regs * | spi | ) |

Enables transmit parity.

This API only enables transmit parity, it does not configure the parity mode used.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disableTransmitParity | ( | SPI_Regs * | spi | ) |

Disables transmit parity.

This API only disables transmit parity, it does not configure the parity mode used.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isTransmitParityEnabled | ( | SPI_Regs * | spi | ) |

Checks if transmit parity is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | Transmit parity is enabled |

| false | Transmit parity is disabled |

| __STATIC_INLINE void DL_SPI_setFrameFormat | ( | SPI_Regs * | spi, |

| DL_SPI_FRAME_FORMAT | frameFormat | ||

| ) |

Set the frame format to use.

Configures the frame format to use for transactions. If you are using chip select you must use one of the Motorola 4 wire frame formats.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | frameFormat | Frame format to use. One of DL_SPI_FRAME_FORMAT. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_FRAME_FORMAT DL_SPI_getFrameFormat | ( | SPI_Regs * | spi | ) |

Get the frame format configuration.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_FRAME_FORMAT |

| __STATIC_INLINE void DL_SPI_setDataSize | ( | SPI_Regs * | spi, |

| DL_SPI_DATA_SIZE | dataSize | ||

| ) |

Set the size for transfers.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | dataSize | Number of bits used in a transfer. One of DL_SPI_DATA_SIZE |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_DATA_SIZE DL_SPI_getDataSize | ( | SPI_Regs * | spi | ) |

Get the configured size for transfers.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_DATA_SIZE |

| __STATIC_INLINE void DL_SPI_setMode | ( | SPI_Regs * | spi, |

| DL_SPI_MODE | mode | ||

| ) |

Set whether the device should be in controller/peripheral mode.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | mode | Mode to configure the SPI into. One of DL_SPI_MODE. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_MODE DL_SPI_getMode | ( | SPI_Regs * | spi | ) |

Get the current mode for the SPI (controller/peripheral)

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_MODE. |

| __STATIC_INLINE void DL_SPI_setBitOrder | ( | SPI_Regs * | spi, |

| DL_SPI_BIT_ORDER | bitOrder | ||

| ) |

Set the bit order used for transfers.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | bitOrder | Order for bits to be sent out during transfer. One of DL_SPI_BIT_ORDER. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_BIT_ORDER DL_SPI_getBitOrder | ( | SPI_Regs * | spi | ) |

Get the current bit order used for transfers.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_BIT_ORDER. |

| __STATIC_INLINE void DL_SPI_enableLoopbackMode | ( | SPI_Regs * | spi | ) |

Enables loopback mode.

Enables the loopback mode. When enabled, the output of the transmit serial shifter is connected to the input of the receive serial shifter internally.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disableLoopbackMode | ( | SPI_Regs * | spi | ) |

Disables loopback mode.

Disables the loopback mode. When disabled, the transmit serial shifter and receive serial shifter are not connected internally.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isLoopbackModeEnabled | ( | SPI_Regs * | spi | ) |

Checks if the loopback mode is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | if loopback mode is enabled |

| false | if loopback mode is disabled |

| __STATIC_INLINE void DL_SPI_setRepeatTransmit | ( | SPI_Regs * | spi, |

| uint32_t | numRepeats | ||

| ) |

Set counter for repeated transmit.

Repeated transmit allows you to send the same data multiple times. This is essentially the same as writing the data into the transmit buffer repeatedly.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | numRepeats | number of times to repeat the transfer. Should be a value between 0-255.

|

References DL_Common_updateReg().

| __STATIC_INLINE uint32_t DL_SPI_getRepeatTransmit | ( | SPI_Regs * | spi | ) |

Get counter for repeated transmit.

Repeated transmit allows you to send the same data multiple times. This is essentially the same as writing the data into the transmit buffer repeatedly.

| [in] | spi | pointer to the register overlay for the peripheral |

| 0 | Repeated transfer is disabled |

| 1-255 | Repeat that many times. |

| __STATIC_INLINE void DL_SPI_enablePeripheralAlignDataOnChipSelect | ( | SPI_Regs * | spi | ) |

Enables data alignment on chip select for peripherals.

When enabled, the receieve bit counter is cleared automatically when the chip select gets set inactive. This helps the peripheral synchronize again to the controller in case of a disturbance or glitch on the clock line or during initialization.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disablePeripheralAlignDataOnChipSelect | ( | SPI_Regs * | spi | ) |

Disables data alignment on chip select for peripherals.

When disable, the receieve bit counter is not cleared automatically when the chip select gets set inactive.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isPeripheralAlignDataOnChipSelectEnabled | ( | SPI_Regs * | spi | ) |

Checks if data alignment on chip select for peripherals is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | Data alignment on chip select is enabled |

| false | Data alignment on chip select is disabled |

| __STATIC_INLINE void DL_SPI_enablePacking | ( | SPI_Regs * | spi | ) |

Enables packing feature.

When enabled, two entries of the RX FIFO are returned as a 32-bit value. When reading the TX FIFO, if the last write to that field was a 32-bit write, those 32-bits will be returned. When writing to the TX FIFO, a 32-bit write will be written as one FIFO entry.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disablePacking | ( | SPI_Regs * | spi | ) |

Disables packing feature.

When disabled, 1 entry of the RX FIFO is returned as a 16-bit value. When reading the TX FIFO, if the last write to that field was a 16-bit write, those 16-bits wil be returned. When writing to the TX FIFO, a 32-bit write will be written as two FIFO entries.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isPackingEnabled | ( | SPI_Regs * | spi | ) |

Checks if packing feature is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | Packing is enabled |

| false | Packing is disabled |

| __STATIC_INLINE void DL_SPI_setChipSelect | ( | SPI_Regs * | spi, |

| DL_SPI_CHIP_SELECT | chipSelect | ||

| ) |

Set chip select used for controller or peripheral mode.

Choose which chip select should be used for data transfer. User must ensure one of the 4-wire frame formats were selected using DL_SPI_init or DL_SPI_setFrameFormat.

This API is for both controller and peripheral modes, and the chip select can be changed in the application by calling this API.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | chipSelect | the chip select pin to use. One of DL_SPI_CHIP_SELECT. |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_CHIP_SELECT DL_SPI_getChipSelect | ( | SPI_Regs * | spi | ) |

Get chip select used for controller or peripheral mode.

This API is for both controller and peripheral modes.

| [in] | spi | pointer to the register overlay for the peripheral |

| One | of DL_SPI_CHIP_SELECT. |

| __STATIC_INLINE void DL_SPI_setPeripheralReceiveTimeout | ( | SPI_Regs * | spi, |

| uint32_t | timeout | ||

| ) |

Set peripheral receive timeout.

Sets the number of clock cycles before a receive timeout occurs.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | timeout | Number of clock cycles before a receive timeout occurs. Must be between 0-63.

|

References DL_Common_updateReg().

| __STATIC_INLINE uint32_t DL_SPI_getPeripheralReceiveTimeout | ( | SPI_Regs * | spi | ) |

Get peripheral receive timeout.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| 0 | indicating that receive timeout is disabled |

| 1-63 | number of clock cycles before a receive timeout occurs |

| __STATIC_INLINE void DL_SPI_setControllerCommandDataModeConfig | ( | SPI_Regs * | spi, |

| uint32_t | config | ||

| ) |

Configure the command/data mode.

Command/data mode allows the hardware to control the C/D pin to indicate whether the data being transferred is a command or just data. The C/D pin is low for commands and high for data.

You can use this API to manually set the C/D pin by passing in DL_SPI_CD_MODE_DATA or DL_SPI_CD_MODE_COMMAND. You can also have the C/D pin switch automatically by passing in how many bytes are part of the command transfer. The C/D pin will stay low until that many bytes are sent out and then automatically switch to high.

This is only relevant when in controller mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | config | configuration for command/data mode. One of:

|

References DL_Common_updateReg().

| __STATIC_INLINE uint32_t DL_SPI_getControllerCommandDataModeConfig | ( | SPI_Regs * | spi | ) |

Get the command/data mode configuration.

Returns the current configuration for command/data mode. When using the automatic C/D pin the value read back will be the number of command bytes remaining to be sent.

| [in] | spi | pointer to the register overlay for the peripheral |

| DL_SPI_CD_MODE_DATA | if in manual data mode |

| DL_SPI_CD_MODE_COMMAND | if in manual command mode |

| 1-14 | indicating how many command bytes still need to be sent |

| __STATIC_INLINE void DL_SPI_enableControllerCommandDataMode | ( | SPI_Regs * | spi | ) |

Enables command/data mode.

When command/data mode is enabled, the C/D pin is used to differentiate between command and data during the transaction.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disableControllerCommandDataMode | ( | SPI_Regs * | spi | ) |

Disables command/data mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isControllerCommandDataModeEnabled | ( | SPI_Regs * | spi | ) |

Checks if command/data mode is enabled.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | Command/data mode is enabled |

| false | Command/data mode is disabled |

| __STATIC_INLINE void DL_SPI_enablePeripheralDataOutput | ( | SPI_Regs * | spi | ) |

Enables peripheral data output.

When peripheral data output is enabled, the peripheral can drive the POCI output pin. This will cause problems if all peripherals have their RXD lines tied together and the controller is trying to broadcast a message to all peripherals while ensuring only one peripheral drives data onto its serial output line.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disablePeripheralDataOutput | ( | SPI_Regs * | spi | ) |

Disables peripheral data output.

When peripheral data output is disabled, the peripheral cannot drive the POCI output pin. This allows multiple peripherals that have their RXD lines tied together to receive a broadcasted message from a controller.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE bool DL_SPI_isPeripheralDataOutputEnabled | ( | SPI_Regs * | spi | ) |

Checks if peripheral data output is enabled.

This is only relevant when in peripheral mode.

| [in] | spi | pointer to the register overlay for the peripheral |

| true | if peripheral data output is enabled |

| false | if peripheral data output is disabled |

| __STATIC_INLINE void DL_SPI_setDelayedSampling | ( | SPI_Regs * | spi, |

| uint32_t | delay | ||

| ) |

Set the delay sampling.

In controller mode only, the data on the input pin will be delayed sampled by the defined SPI clock cycles. The delay can be adjusted in steps of SPI input clock steps. The maximum allowed delay should not exceed the length of one data frame

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | delay | The number of SPI clock cycles to delay sampling on input pin. Value between 0-15. |

References DL_Common_updateReg().

| __STATIC_INLINE uint32_t DL_SPI_getDelayedSampling | ( | SPI_Regs * | spi | ) |

Get the delay sampling.

In controller mode only, the data on the input pin will be delayed sampled by the defined SPI clock cycles. The delay can be adjusted in steps of SPI input clock steps. The maximum allowed delay should not exceed the length of one data frame

| [in] | spi | Pointer to the register overlay for the peripheral |

| 0 | - 15. The amount of delay sampling in SPI clock cycles. |

| __STATIC_INLINE void DL_SPI_setFIFOThreshold | ( | SPI_Regs * | spi, |

| DL_SPI_RX_FIFO_LEVEL | rxThreshold, | ||

| DL_SPI_TX_FIFO_LEVEL | txThreshold | ||

| ) |

Set the RX and TX FIFO interrupt threshold level.

Select the threshold for the receive and transmit FIFO interrupts. The interrupts are generated based on a transition through a level rather than being based on the level. That is, the interrupts are generated when the fill level progresses through the trigger level.

For example, if the trigger level is set to the half-way mark, the interrupt is triggered when the FIFO becomes half empty/full.

Out of reset, the FIFOs are triggered to interrupt at half-way mark.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | rxThreshold | One of DL_SPI_RX_FIFO_LEVEL |

| [in] | txThreshold | One of DL_SPI_TX_FIFO_LEVEL |

References DL_Common_updateReg().

| __STATIC_INLINE DL_SPI_TX_FIFO_LEVEL DL_SPI_getTXFIFOThreshold | ( | SPI_Regs * | spi | ) |

Get the TX FIFO interrupt threshold level.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_TX_FIFO_LEVEL |

| __STATIC_INLINE DL_SPI_RX_FIFO_LEVEL DL_SPI_getRXFIFOThreshold | ( | SPI_Regs * | spi | ) |

Get the RX FIFO interrupt threshold level.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_RX_FIFO_LEVEL |

| __STATIC_INLINE void DL_SPI_setBitRateSerialClockDivider | ( | SPI_Regs * | spi, |

| uint32_t | SCR | ||

| ) |

Set the SPI bit rate serial clock divider (SCR)

The SPI includes a programmable bit rate clock divider and prescaler to generate the serial output clock. The bit rates are supported up to FUNCCLK/2. The functional clock selection depends on the specific device, please refer to the device datasheet and PMU/Clock section.

The SPI output bit rate is calculated with the following formula: SPI bit rate = (SPI functional clock) / ((1 + SCR)*2) Given this formula, the SCR can be calculated: SCR = (SPI functional clock) / ((2 * SPI bit rate) - 1)

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | SCR | The SPI serial clock divider. Value between 0-1023. |

References DL_Common_updateReg().

| __STATIC_INLINE uint32_t DL_SPI_getBitRateSerialClockDivider | ( | SPI_Regs * | spi | ) |

Get the SPI bit rate serial clock divider (SCR)

| [in] | spi | Pointer to the register overlay for the peripheral |

| The | SPI SCR. Value from 0-1023 |

| __STATIC_INLINE void DL_SPI_transmitData8 | ( | SPI_Regs * | spi, |

| uint8_t | data | ||

| ) |

Writes 8-bit data into the TX FIFO for transmit.

Puts the data into the TX FIFO without checking its status. Use if already sure the TX FIFO has space for the write. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| __STATIC_INLINE void DL_SPI_transmitData16 | ( | SPI_Regs * | spi, |

| uint16_t | data | ||

| ) |

Writes 16-bit data into the TX FIFO for transmit.

Puts the data into the TX FIFO without checking its status. Use if already sure the TX FIFO has space for the write. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| __STATIC_INLINE void DL_SPI_transmitData32 | ( | SPI_Regs * | spi, |

| uint32_t | data | ||

| ) |

Writes 32-bit data into the TX FIFO for transmit.

Puts the data into the TX FIFO without checking its status. Use if already sure the TX FIFO has space for the write. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: If packing is enabled by calling DL_SPI_enablePacking prior to calling this API, then a 32-bit write will be written as one FIFO entry. If packing is disabled, then a 32-bit write will be written as two FIFO entries.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| __STATIC_INLINE uint8_t DL_SPI_receiveData8 | ( | SPI_Regs * | spi | ) |

Reads 8-bit data from the RX FIFO.

Reads the data from the RX FIFO without checking its status. Use if already sure the RX FIFO has data available. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE uint16_t DL_SPI_receiveData16 | ( | SPI_Regs * | spi | ) |

Reads 16-bit data from the RX FIFO.

Reads the data from the RX FIFO without checking its status. Use if already sure the RX FIFO has data available. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE uint32_t DL_SPI_receiveData32 | ( | SPI_Regs * | spi | ) |

Reads 32-bit data from the RX FIFO.

Reads the data from the RX FIFO without checking its status. Use if already sure the RX FIFO has data available. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: Requires that packing has been enabled by calling DL_SPI_enablePacking prior to calling this API. When packing is enabled, two entries of the RX FIFO are returned as a 32-bit value.

| [in] | spi | pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_enableInterrupt | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Enable SPI interrupts.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to enable. Bitwise OR of DL_SPI_INTERRUPT. |

| __STATIC_INLINE void DL_SPI_disableInterrupt | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Disable SPI interrupts.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to disable. Bitwise OR of DL_SPI_INTERRUPT. |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledInterrupts | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check which SPI interrupts are enabled.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_INTERRUPT. |

| Bitwise | OR of DL_SPI_INTERRUPT values |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledInterruptStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check interrupt flag of enabled SPI interrupts.

Checks if any of the SPI interrupts that were previously enabled are pending.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_INTERRUPT. |

| Bitwise | OR of DL_SPI_INTERRUPT values |

| __STATIC_INLINE uint32_t DL_SPI_getRawInterruptStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check interrupt flag of any SPI interrupt.

Checks if any of the SPI interrupts are pending. Interrupts do not have to be previously enabled.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_INTERRUPT. |

| Bitwise | OR of DL_SPI_INTERRUPT values |

| __STATIC_INLINE DL_SPI_IIDX DL_SPI_getPendingInterrupt | ( | SPI_Regs * | spi | ) |

Get highest priority pending SPI interrupt.

Checks if any of the SPI interrupts are pending. Interrupts do not have to be previously enabled.

| [in] | spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_clearInterruptStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Clear pending SPI interrupts.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to clear. Bitwise OR of DL_SPI_INTERRUPT. |

References DL_SPI_drainRXFIFO16(), DL_SPI_drainRXFIFO32(), DL_SPI_drainRXFIFO8(), DL_SPI_fillTXFIFO16(), DL_SPI_fillTXFIFO32(), DL_SPI_fillTXFIFO8(), DL_SPI_receiveDataBlocking16(), DL_SPI_receiveDataBlocking32(), DL_SPI_receiveDataBlocking8(), DL_SPI_receiveDataCheck16(), DL_SPI_receiveDataCheck32(), DL_SPI_receiveDataCheck8(), DL_SPI_transmitDataBlocking16(), DL_SPI_transmitDataBlocking32(), DL_SPI_transmitDataBlocking8(), DL_SPI_transmitDataCheck16(), DL_SPI_transmitDataCheck32(), and DL_SPI_transmitDataCheck8().

| void DL_SPI_transmitDataBlocking8 | ( | SPI_Regs * | spi, |

| uint8_t | data | ||

| ) |

Blocks to ensure transmit is ready before sending data.

Puts the data into the TX FIFO after blocking to ensure the TX FIFO is not full. Will wait indefinitely until there is space in the TX FIFO. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

Referenced by DL_SPI_clearInterruptStatus().

| void DL_SPI_transmitDataBlocking16 | ( | SPI_Regs * | spi, |

| uint16_t | data | ||

| ) |

Blocks to ensure transmit is ready before sending data.

Puts the data into the TX FIFO after blocking to ensure the TX FIFO is not full. Will wait indefinitely until there is space in the TX FIFO. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

Referenced by DL_SPI_clearInterruptStatus().

| void DL_SPI_transmitDataBlocking32 | ( | SPI_Regs * | spi, |

| uint32_t | data | ||

| ) |

Blocks to ensure transmit is ready before sending data.

Puts the data into the TX FIFO after blocking to ensure the TX FIFO is not full. Will wait indefinitely until there is space in the TX FIFO. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: If packing is enabled by calling DL_SPI_enablePacking prior to calling this API, then a 32-bit write will be written as one FIFO entry. If packing is disabled, then a 32-bit write will be written as two FIFO entries.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

Referenced by DL_SPI_clearInterruptStatus().

| uint8_t DL_SPI_receiveDataBlocking8 | ( | SPI_Regs * | spi | ) |

Blocks to ensure receive is ready before reading data.

Reads the data from the RX FIFO after blocking to ensure the RX FIFO is not empty. Will wait indefinitely until there is data in the RX FIFO. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

Referenced by DL_SPI_clearInterruptStatus().

| uint16_t DL_SPI_receiveDataBlocking16 | ( | SPI_Regs * | spi | ) |

Blocks to ensure receive is ready before reading data.

Reads the data from the RX FIFO after blocking to ensure the RX FIFO is not empty. Will wait indefinitely until there is data in the RX FIFO. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_receiveDataBlocking32 | ( | SPI_Regs * | spi | ) |

Blocks to ensure receive is ready before reading data.

Reads the data from the RX FIFO after blocking to ensure the RX FIFO is not empty. Will wait indefinitely until there is data in the RX FIFO. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: Requires that packing has been enabled by calling DL_SPI_enablePacking prior to calling this API. When packing is enabled, two entries of the RX FIFO are returned as a 32-bit value.

| [in] | spi | pointer to the register overlay for the peripheral |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_transmitDataCheck8 | ( | SPI_Regs * | spi, |

| uint8_t | data | ||

| ) |

Checks the TX FIFO before trying to transmit data.

Checks if the TX FIFO is already full before trying to add new data to the FIFO. Exits immediately if full rather than trying to block. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| true | if data was added to the TX FIFO |

| false | if the TX FIFO was full and data was not added |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_transmitDataCheck16 | ( | SPI_Regs * | spi, |

| uint16_t | data | ||

| ) |

Checks the TX FIFO before trying to transmit data.

Checks if the TX FIFO is already full before trying to add new data to the FIFO. Exits immediately if full rather than trying to block. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| true | if data was added to the TX FIFO |

| false | if the TX FIFO was full and data was not added |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_transmitDataCheck32 | ( | SPI_Regs * | spi, |

| uint32_t | data | ||

| ) |

Checks the TX FIFO before trying to transmit data.

Checks if the TX FIFO is already full before trying to add new data to the FIFO. Exits immediately if full rather than trying to block. See related APIs for additional transmit options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: If packing is enabled by calling DL_SPI_enablePacking prior to calling this API, then a 32-bit write will be written as one FIFO entry. If packing is disabled, then a 32-bit write will be written as two FIFO entries.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | data | data to send |

| true | if data was added to the TX FIFO |

| false | if the TX FIFO was full and data was not added |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_receiveDataCheck8 | ( | SPI_Regs * | spi, |

| uint8_t * | buffer | ||

| ) |

Checks the RX FIFO before trying to transmit data.

Checks if the RX FIFO is already empty before trying to read new data from the FIFO. Exits immediately if empty rather than trying to block. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 8 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | buffer | a buffer to write the received data into |

| true | if data was read from the RX FIFO |

| false | if the RX FIFO was empty and data was not read |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_receiveDataCheck16 | ( | SPI_Regs * | spi, |

| uint16_t * | buffer | ||

| ) |

Checks the RX FIFO before trying to transmit data.

Checks if the RX FIFO is already empty before trying to read new data from the FIFO. Exits immediately if empty rather than trying to block. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 16 bits.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | buffer | a buffer to write the received data into |

| true | if data was read from the RX FIFO |

| false | if the RX FIFO was empty and data was not read |

Referenced by DL_SPI_clearInterruptStatus().

| bool DL_SPI_receiveDataCheck32 | ( | SPI_Regs * | spi, |

| uint32_t * | buffer | ||

| ) |

Checks the RX FIFO before trying to transmit data.

Checks if the RX FIFO is already empty before trying to read new data from the FIFO. Exits immediately if empty rather than trying to block. See related APIs for additional receive options.

Can be used for any data transfers that are less than or equal to 32 bits.

NOTE: Requires that packing has been enabled by calling DL_SPI_enablePacking prior to calling this API. When packing is enabled, two entries of the RX FIFO are returned as a 32-bit value.

| [in] | spi | pointer to the register overlay for the peripheral |

| [in] | buffer | a buffer to write the received data into |

| true | if data was read from the RX FIFO |

| false | if the RX FIFO was empty and data was not read |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_drainRXFIFO8 | ( | SPI_Regs * | spi, |

| uint8_t * | buffer, | ||

| uint32_t | maxCount | ||

| ) |

Read all available data out of the RX FIFO using 8 bit access.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [out] | buffer | Buffer to write received data into |

| [in] | maxCount | Max number of bytes to read from the RX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_drainRXFIFO16 | ( | SPI_Regs * | spi, |

| uint16_t * | buffer, | ||

| uint32_t | maxCount | ||

| ) |

Read all available data out of the RX FIFO using 16 bit access.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [out] | buffer | Buffer to write received data into |

| [in] | maxCount | Max number of halfwords to read from the RX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_drainRXFIFO32 | ( | SPI_Regs * | spi, |

| uint32_t * | buffer, | ||

| uint32_t | maxCount | ||

| ) |

Read all available data out of the RX FIFO using 32 bit access.

NOTE: Requires that packing has been enabled by calling DL_SPI_enablePacking prior to calling this API. When packing is enabled, two entries of the RX FIFO are returned as a 32-bit value.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [out] | buffer | Buffer to write received data into |

| [in] | maxCount | Max number of words to read from the RX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_fillTXFIFO8 | ( | SPI_Regs * | spi, |

| uint8_t * | buffer, | ||

| uint32_t | count | ||

| ) |

Fill the TX FIFO using 8 bit access.

Continuously write data into the TX FIFO until it is filled up or count has been reached.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | buffer | Buffer of data to write to the TX FIFO |

| [in] | count | Max number of bytes to write to the TX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_fillTXFIFO16 | ( | SPI_Regs * | spi, |

| uint16_t * | buffer, | ||

| uint32_t | count | ||

| ) |

Fill the TX FIFO using 16 bit access.

Continuously write data into the TX FIFO until it is filled up or count has been reached.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | buffer | Buffer of data to write to the TX FIFO |

| [in] | count | Max number of halfwords to write to the TX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| uint32_t DL_SPI_fillTXFIFO32 | ( | SPI_Regs * | spi, |

| uint32_t * | buffer, | ||

| uint32_t | count | ||

| ) |

Fill the TX FIFO using 32 bit access.

Continuously write data into the TX FIFO until it is filled up or count has been reached.

NOTE: If packing is enabled by calling DL_SPI_enablePacking prior to calling this API, then a 32-bit write will be written as one FIFO entry. If packing is disabled, then a 32-bit write will be written as two FIFO entries.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | buffer | Buffer of data to write to the TX FIFO |

| [in] | count | Max number of words to write to the TX FIFO |

Referenced by DL_SPI_clearInterruptStatus().

| __STATIC_INLINE void DL_SPI_enableDMAReceiveEvent | ( | SPI_Regs * | spi, |

| uint32_t | interrupt | ||

| ) |

Enable SPI interrupt for triggering the DMA receive event.

Enables the SPI interrupt to be used as the condition to generate an event to directly trigger the DMA. This API configures the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interrupt | Interrupt to enable as the trigger condition for the DMA. One of DL_SPI_DMA_INTERRUPT_RX. |

| __STATIC_INLINE void DL_SPI_enableDMATransmitEvent | ( | SPI_Regs * | spi | ) |

Enable SPI interrupt for triggering the DMA transmit event.

Enables the SPI interrupt to be used as the condition to generate an event to directly trigger the DMA. This API configures the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE void DL_SPI_disableDMAReceiveEvent | ( | SPI_Regs * | spi, |

| uint32_t | interrupt | ||

| ) |

Disables SPI interrupt from triggering the DMA receive event.

Disables the SPI interrupt as the condition to generate an event to directly trigger the DMA. This API configures the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interrupt | Interrupt to disable as the trigger condition for the DMA. One of DL_SPI_DMA_INTERRUPT_RX. |

| __STATIC_INLINE void DL_SPI_disableDMATransmitEvent | ( | SPI_Regs * | spi | ) |

Disables SPI interrupt from triggering the DMA transmit event.

Disables the SPI interrupt as the condition to generate an event to directly trigger the DMA. This API configures the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledDMAReceiveEvent | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check which SPI interrupt for DMA receive events is enabled.

This API checks the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_DMA_INTERRUPT_RX. |

| One | of DL_SPI_DMA_INTERRUPT_RX |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledDMATransmitEvent | ( | SPI_Regs * | spi | ) |

Check if SPI interrupt for DMA transmit event is enabled.

This API checks the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| DL_SPI_DMA_INTERRUPT_TX | if enabled, 0 if not enabled |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledDMAReceiveEventStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check interrupt flag of enabled SPI interrupt for DMA receive event.

Checks if any of the SPI interrupts for the DMA receive event that were previously enabled are pending. This API checks the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_DMA_INTERRUPT_RX. |

| One | of DL_SPI_DMA_INTERRUPT_RX |

| __STATIC_INLINE uint32_t DL_SPI_getEnabledDMATransmitEventStatus | ( | SPI_Regs * | spi | ) |

Check interrupt flag of enabled SPI interrupt for DMA transmit event.

Checks if the SPI interrupt for the DMA transmit event that was previously enabled is pending. This API checks the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| DL_SPI_DMA_INTERRUPT_TX | if enabled, 0 if not enabled |

| __STATIC_INLINE uint32_t DL_SPI_getRawDMAReceiveEventStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Check interrupt flag of any SPI interrupt for DMA receive event.

Checks if any of the SPI interrupts for DMA receive event are pending. Interrupts do not have to be previously enabled. This API checks the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to check. Bitwise OR of DL_SPI_DMA_INTERRUPT_RX. |

| Bitwise | OR of DL_SPI_DMA_INTERRUPT_RX values |

| __STATIC_INLINE uint32_t DL_SPI_getRawDMATransmitEventStatus | ( | SPI_Regs * | spi | ) |

Check interrupt flag of any SPI interrupt for DMA transmit event.

Checks if any of the SPI interrupts for DMA transmit event are pending. Interrupts do not have to be previously enabled. This API checks the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| DL_SPI_DMA_INTERRUPT_TX | if enabled, 0 if not enabled |

| __STATIC_INLINE DL_SPI_DMA_IIDX_RX DL_SPI_getPendingDMAReceiveEvent | ( | SPI_Regs * | spi | ) |

Get highest priority pending SPI interrupt for DMA receive event.

Checks if any of the SPI interrupts for DMA receive event are pending. Interrupts do not have to be previously enabled. This API checks the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| One | of DL_SPI_DMA_IIDX_RX |

| __STATIC_INLINE DL_SPI_DMA_IIDX_TX DL_SPI_getPendingDMATransmitEvent | ( | SPI_Regs * | spi | ) |

Get highest priority pending SPI interrupt for DMA transmit event.

Checks if the SPI interrupt for DMA transmit event is pending. Interrupts do not have to be previously enabled. This API checks the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| DL_SPI_DMA_IIDX_TX | if pending, 0 if not pending |

| __STATIC_INLINE void DL_SPI_clearDMAReceiveEventStatus | ( | SPI_Regs * | spi, |

| uint32_t | interruptMask | ||

| ) |

Clear pending SPI interrupts for DMA receive event.

This API checks the DMA_TRIG_RX register, which is the event publisher used for triggering the DMA to do a receive data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | interruptMask | Bit mask of interrupts to clear. Bitwise OR of DL_SPI_DMA_INTERRUPT_RX. |

| __STATIC_INLINE void DL_SPI_clearDMATransmitEventStatus | ( | SPI_Regs * | spi | ) |

Clear pending SPI interrupt for DMA transmit event.

This API checks the DMA_TRIG_TX register, which is the event publisher used for triggering the DMA to do a transmit data transfer.

| [in] | spi | Pointer to the register overlay for the peripheral |

References DL_SPI_restoreConfiguration(), and DL_SPI_saveConfiguration().

| bool DL_SPI_saveConfiguration | ( | SPI_Regs * | spi, |

| DL_SPI_backupConfig * | ptr | ||

| ) |

Save SPI configuration before entering a power loss state.

Some MSPM0G peripherals residing in PD1 domain do not retain register contents when entering STOP or STANDBY modes. Please refer to the datasheet for the full list of peripheral instances that exhibit this behavior.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | ptr | Configuration backup setup structure. See DL_SPI_backupConfig. |

| FALSE | if a configuration already exists in ptr (will not be overwritten). TRUE if a configuration was successfully saved |

Referenced by DL_SPI_clearDMATransmitEventStatus().

| bool DL_SPI_restoreConfiguration | ( | SPI_Regs * | spi, |

| DL_SPI_backupConfig * | ptr | ||

| ) |

Restore SPI configuration after leaving a power loss state.

Some MSPM0G peripherals residing in PD1 domain do not retain register contents when entering STOP or STANDBY modes. Please refer to the datasheet for the full list of peripheral instances that exhibit this behavior.

| [in] | spi | Pointer to the register overlay for the peripheral |

| [in] | ptr | Configuration backup setup structure. See DL_SPI_backupConfig. |

| FALSE | if a configuration does not exist in ptr (will not be loaded). TRUE if a configuration successfully loaded |

Referenced by DL_SPI_clearDMATransmitEventStatus().